- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

分析PLL带宽对高速串行数据眼 测试结果的影响

CDR与PLL简介

PLL的作用简单的来说是产生一个内部信号,去锁住输入信号的相位。讨论两个信号相位的前提是该两个信号的频率一致,这样才有意义,因此锁相环也是锁频回路。假定一固定频率信号:

输入PLL,PLL的输出信号为:

由上述结论得到:

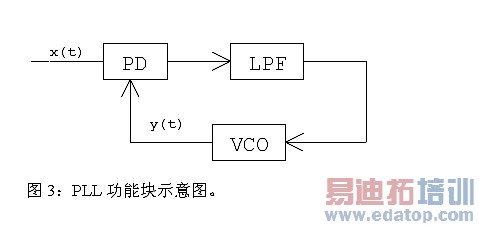

但相位是否相等呢?答案是否定的。实际上,两个信号的相位差是一个定值,其值和起始频率差有关。所以有了第二个重要概念:“锁相不是指相位相同,而是相位差为定值”。PLL的组成如图3所示。

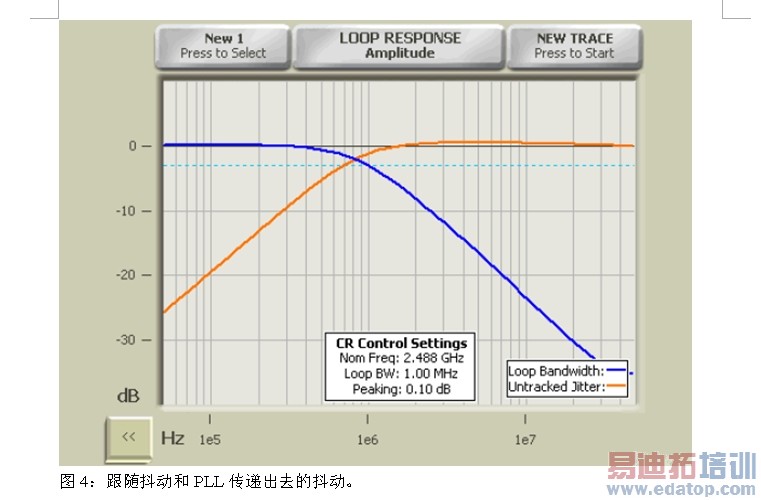

鉴相器(PD)将输入信号与VCO(压控振荡器)输出信号进行对比。环路滤波器对差异进行过滤波,然后用来调整VCO。由于LPF是低通滤波器,只能将相位差的低频部分传输到VCO。因此,PLL仅跟踪低频变化。也就是说,由串行数据的CDR电路恢复得到的Recover Clock只包含低频抖动,这个低频抖动在数据中同时存在,因此这些低频抖动成分对于接收端SerDes电路在以Recover Clock作为参考边沿判决数据0或1时不会产生影响(前提条件是低频抖动分量不得超过系统的抖动容限)。而数据中还包含传输系统中的高频抖动分量,由于CDR电路中的低通滤波器的缘故,这部分恢复出的Clock是不包含的。因此接收端SerDes电路在以Recover Clock作为参考边沿判决数据0或1时可能会由于这些高频的抖动分量导致采样点偏移而出现误码。因此只有在PLL截止频率或带宽以下的低频抖动是接收端可以跟随的抖动。相对而言,经过PLL传递出的抖动都为高频抖动,是不能被系统跟随的,会导致接收端采样点的偏移产生误码。如下图所示,蓝色线为PLL的幅频特性曲线,其下面包含的区域即为系统可以跟随的抖动。对应的橙色曲线表示传递出去的抖动的幅频趋势。

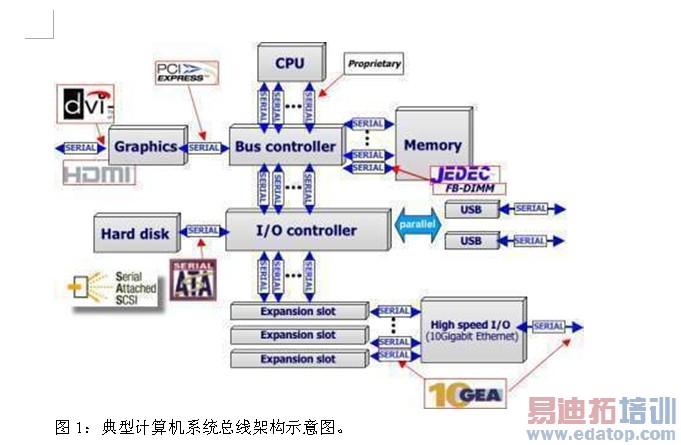

图1:典型计算机系统总线架构示意图。

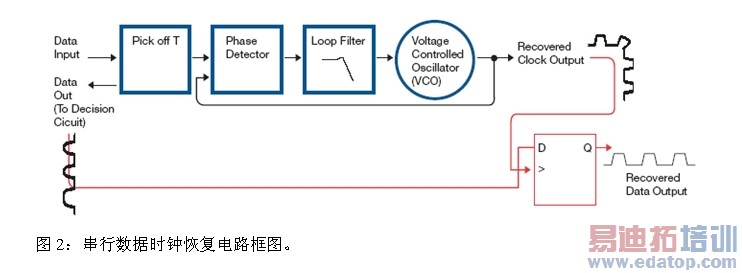

图2:串行数据时钟恢复电路框图。

图3:PLL功能块示意图。

图4:跟随抖动和PLL传递出去的抖动。

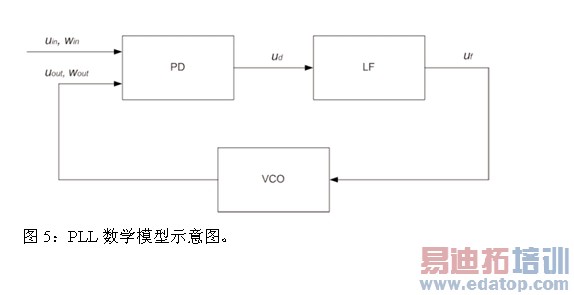

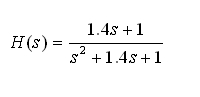

如果对图5的PLL建立数学模型和分析,每个功能块均可以用传递函数表示。

图5:PLL数学模型示意图。

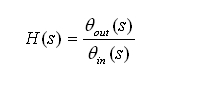

通常使用两种闭环路传递函数。一种是相位传递函数,定义如下:

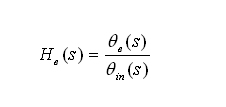

另一种是误差传递函数,定义如下:

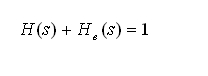

相位传递函数为低通,而误差传递函数为高通。两者关系如下:

该公式用于计算复值。因为复值有幅度和相位,因此该公式并不代表两个传递函数的复值之和为1。

当前应用比较普遍的串行数据中CDR采用一阶PLL较多,比如GBE,SATA 1.5Gb/s,PCI-ExpressI 2.5Gb/s,以及XAUI 3.125Gb/s。随着技术的发展,在DisplayPort及PCI-Express II 5.0Gb/s等一些新标准中二阶PLL也开始得到了应用。

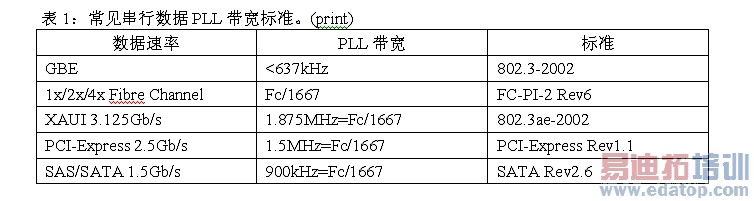

在当前的大多数主流串行数据标准中,其CDR一般采用指定带宽的“Golden PLL”或采用单极点、高通、20dB/dc滚降、截止频率或带宽等于数据速率/1667这样一些特征的PLL进行时钟恢复。表1是常见串行数据CDR中采用的PLL带宽及标准。

表1:常见串行数据PLL带宽标准。