- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

WLR测试中所面临的新挑战

随着引入的化合物材料的增加,可靠性方面的挑战继续加大。这些新挑战意味着可靠性测试日趋艰难,目前的测试设备已无法满足。在现有设备的能力与尚未满足的测试需求之间,可靠性和质保方面的工程师和研究人员正在面临日见扩大的差距。这种情况下要求测试仪器提供商和处于可靠性测试技术前沿的客户之间进一步通力合作。

可靠性测试发展趋势

目前业界正在寻求新型的半导体门介质材料,来解决超薄门所导致的漏电流增加。随着一些非常规的介电材料的引入,例如二氧化铪,此时众所周知的偏置温度不稳定(BTI)这类退化机制就变成非常严重的问题。固然,这些新材料可以降低门泄漏,从而降低静态工作点,但也导致门限电压和基带电压不稳定的问题。

除BTI之外,新一代的门堆叠(特别是高K金属门)显示时间取决于介质击穿(TDDB)特性,这与传统的SiO2材料极大不同。先前用于硬击穿和软击穿的模型比较好理解,然而这些新材料则呈现“渐进击穿(progressive breakdown)”。眼下的迫切任务就是要探索失效机制背后的物理特性的具体细节,随着这些材料进入工艺兼容性正在被优化的工程阶段,这一任务显得日益迫切。这些都要求一类新的测试设备,这些设备不仅要具有较好的测试功能,还要有丰富的处理功率(processing power),以适应创新的测试序列。

许多退化机制都是由阱电荷导致的结果。因此,需要对相对于器件的诱捕和释放(trapping and de-trapping)速率的参数退化量进行测量。测量必须在电应力去掉后迅速完成,而且应力条件还必须在测量完成后尽可能快地恢复。故绝大多数的老式仪器都无法满足这些要求。

此外,很明显,各种晶体管性能增强技术导致了器件可靠性和电路可靠性方面复杂的相互作用。例如,用来提高通道迁移率的应力硅工艺会恶化BTI性能。进一步说,门限电压的不稳定将会导致迁出电流提高,从而导致较高的结温。结温的升高将会加速介质泄漏和击穿。这些高级别的交互作用难以建模,并随机地导致失效。研发可靠的模型就需要相应的测试仪器,以便能够捕获大量的、具备统计意义的带有快速测试序列的测试样本。

电路中的晶体管间的交互作用甚至比单个晶体管内部的工作机制更复杂,故对其建模来说,大的数据集是尤其重要的。例如,P-MOS和N-MOS晶体管的退化方式就不一样。N-MOS容易导致BTI。结果,一个具有互补晶体管的电路来传送时钟信号时,在一个负载周期内或信号转换周期内会产生变化。此外,在不同的退化机制之间也会产生复杂的交互作用。例如,软介质击穿通常会导致泄露增加。尽管这不会导致晶体管彻底失效,但可以加速BTI。由于这些原因,需要捕获大量的具有统计意义的样本数,这意味着征集的数据点多达40000个或更多。

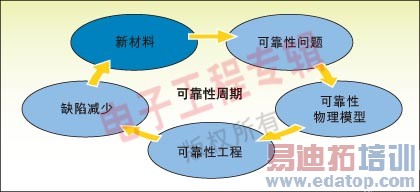

图1:半导体缺陷减少/可靠性改善周期。

图2:多路的MSU不适合控制器件的弛豫时间。

上一篇:正确的电路板布板降低开关模式转换器的EMI

下一篇:高精度直流电压测量的优化