- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用Aldec公司的HES系统快速实现各类IC设计的高级硬件加速仿真

SoC加速软/硬件协同验证

SoC设计中的软/硬件协同验证技术一直以来都是工程师们关注的热点。在传统的SoC开发流程中,软件开发工程师与硬件设计工程师在原型电路板加工完成之前没有交互的过程。软件工程师在软件IDE环境中进行代码的设计与调试。代码调试完成时,软件工程师必须等待原型设计;直到原型电路板加工完成后,才能将软件代码集成到硬件平台上进行软硬件集成测试验证。由于软件开发和硬件设计过程中没有交互,软、硬件设计中的许多bug需要等到软件代码集成到原型电路板中以后才会被发现。在项目设计流程后期阶段才发现的bug往往会给工程师带来巨大的痛苦,很大程度上增加了整个项目的开发周期,同时降低了产品的设计质量。

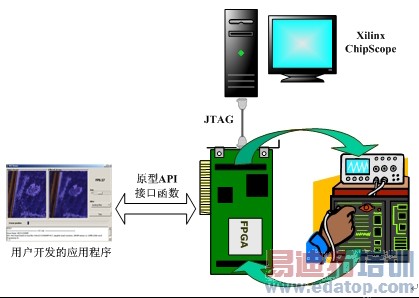

图 4: HES系统中的SoC加速软/硬件协同验证。

软/硬件协同验证的方法能够将软、硬件设计工程师尽早协作在一起。通过软、硬件交互调试将设计中的大部分bug,尤其是软、硬件接口bug消除在开发流程的早期,保证产品的设计质量,并降低了设计反复的风险从而缩短产品的上市时间。

HES系统不仅提供了SoC的软/硬件协同验证能力,同时通过将硬件模型实现到HES硬件加速板和FPGA芯片中最大程度上加快了软/硬件协同验证的速度。

图 5 :使用HES系统快速实现各类IC设计的原型验证平台。

HES系统还能够将ARM或MIPS处理器核的指令存储器指定到不同的位置,以提供不同的取指仿真速度和调试要求。例如用户可以将指令存储器指定放在ARM子板上以获取最快的取指速度;也可以将指令存储器指定到HES硬件加速板上,在较快的取指速度下获得一定的调试能力;用户还可以将指令存储器作为硬件模型放在HDL仿真器里的testbench中以获取最强的指令存储器动作的调试能力。

上一篇:快速实现RoHS/WEEE兼容

下一篇:如何在串扰分析中利用合成电流源建模