- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用Aldec公司的HES系统快速实现各类IC设计的高级硬件加速仿真

除了编写C/C++测试激励程序外,用户还可以编写更高级的应用程序,例如在Visual C++环境中开发带GUI图形界面的高级应用程序。DVM可以自动产生基本的C-Testbench代码,里面包含了基本的API函数调用,例如硬件加速板的初始化函数等。用户可以在此基础上快速开发自定义的C代码。

内部信号的仿真调试

硬件加速仿真的方法通常需要以降低调试能力为代价来获得高速的仿真。HES硬件仿真加速系统不仅仅可以实现高速仿真,还为用户提供了内部信号的调试能力。在DVM工具中,用户可以在RTL级或EDIF网表级指定需要追踪的内部信号,DVM将自动完成代码修改等相关工作。在后续的仿真过程中,这些内部信号与外部信号一样可以进行波形观察、端点设置、信号数据流追踪等操作。

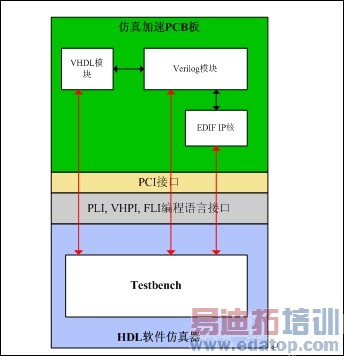

DVM将自动完成图2所示的PCI接口驱动程序的控制,PLI、VHPI、FLI语言接口的编程工作。用户需要做的只是告诉DVM哪些内部信号是需要仿真调试的。

图 2: DVM API接口函数的应用。

设计的自动划分

对于单颗FPGA芯片或单块HES硬件加速电路板无法容纳的大型设计,可以通过在计算机主板上插入多块HES硬件加速板来提供更大容量的FPGA等硬件资源。多块HES硬件加速板最大可以容纳1亿门级的大型设计。

除此之外,DVM工具能够自动完成设计的自动划分。用户只需要指定哪些代码模块实现在哪块HES硬件加速板上,然后由DVM自动完成设计划分,综合,以及最后的布局布线。甚至用户可以不指定划分的方式,由DVM来自动选择哪些代码模块实现在哪块HES硬件加速板上。

图 3:系统设计内部信号的仿真调试。

上一篇:快速实现RoHS/WEEE兼容

下一篇:如何在串扰分析中利用合成电流源建模