- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何在硅芯片制作完成前进行软件开发

在硬件加速器上运行设计时,需要在嵌入式处理器中调试软件。一般这种调试会使用系统可用的硬件接口(例如JTAG接口)连接硬件调试探针来完成。但是有一个问题:尽管JTAG很适合调试功能问题,但很难用它来调试性能和时序问题。因为“混合”虚拟机和仿真的性能更高一筹,你会想在这上面调试所有的功能问题。因此,仅存的问题就是时序和性能相关的问题了。

JTAG和类似的调试技术使处理器进入调试模式,然后使用各种技术来从处理器和外围寄存器中检索数据。即使在最优情况下,这些操作也至少需要耗费成千上万个时钟—通常是数以百万计的时钟。而且这些调试时钟通常只是处理器时钟的一小部分。由于在调试时间点前后调试工具引入了数以百万计的操作时钟的延迟,因此,调试性能和时序问题变得极为困难。开发人员一般通过处理器跟踪来回溯调试,以避免延迟。但即使收集处理器跟踪数据也会影响到你正在观察的系统的运行。

Mentor Graphics有一款产品叫“Codelink”,通过它能收集在仿真中运行设计时的回溯数据,利用这些数据就能驱动传统的软件调试。本质上说,你可以获得传统软件调试中的所有功能—代码单步执行、设立断点,查看内存和变量。这样做保留了仿真系统的时钟周期的精确性,没有任何副作用。你还具有完全的并行多核可见性和运行与回退的能力。但许多性能问题很难在源代码层面调试,通常还需要一幅对比硬件动作的、在设计中运行的处理器的动作时间轴视图。Codelink收集这些跟踪数据,并导入Mentor的系统分析工具,便能对照显示性能数据和硬件数据。要在这一开发阶段对整个设计进行诊断,那么这可能是可视化性能问题和时序问题的最佳解决办法。

FPGA原型通常会比硬件加速器运行得更快,因而更长的软件运行时间是可以实现的,还可能会发现更多设计上的问题。软件调试通常采用JTAG或者类似的技术来实现,但都存在上述的各种问题。在硬件调试中,FPGA历来都存在可视性有限的缺点。FPGA供应商提供的嵌入式逻辑分析仪只能提供有限的跟踪幅度和较浅的跟踪深度以及频繁的重新测量,最终导致漫长、且经常是突然的(“回到原点”)重新编译(综合的和P&R)。这使得在FPGA中调试变得痛苦万分,枯燥不已。幸运的是, 新的技术面市了,不仅能提供成千上万种信号的可见视图,并具备深入跟踪芯片及系统级动作的能力,还能提供前所未有的易用性和强大的运行时可配置性,通过消除大多数重新测量和回头迭代的需求,能极大地提高调试效率。经过改进的调试将对使用FPGA原型的体验和效率产生积极的影响。

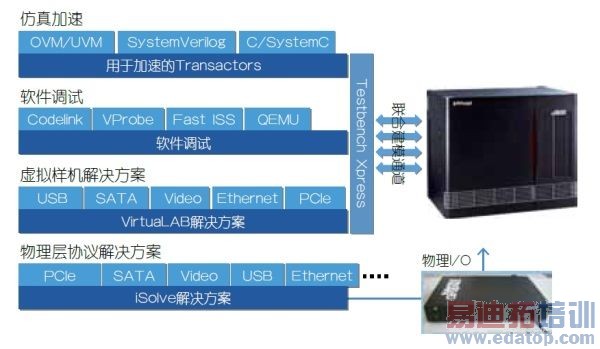

图4:硬件加速器正变得不仅仅只是加速仿真。

从简单的存根代码开始,通过一系列依次更详细和完整的硬件模型来推进,可以在得到实际硬件芯片之前对软件进行验证。你可以长时间保持最高性能能和最易用的调试环境,必要时使用详细的模型验证系统的各个方面。你将需要一个通用的环境来生成、运行和调试,以便和其他环境进行无缝转换。而且这也将扩展到最终的芯片中,因为你会需要对实际产品做一个最终的测试。这意味着一旦你拿到了实体原型,需要做的就仅仅是确认所有功能都正常运行了。针对硬件的抽象模型和后期具有精确时钟周期的RTL硬件模型,最难的软硬件交互问题将在设计阶段就能得以解决。一旦实体样机就绪,就能大大减少软件开发的时间。

作者:Russell Klein

硬件加速器仿真部门技术总监,Mentor Graphics公司

上一篇:开放式FPGA增加测试灵活性

下一篇:探索复杂RF环境中的射频干扰