- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何在硅芯片制作完成前进行软件开发

硬件团队已经创建了可执行的硬件模型,作为正常开发周期的一部分。他们在寄存器传输级(RTL)使用一种硬件描述语言(HDL)来描述自己的设计。最终,通过一系列运行编译器和分析器来运行该设计的HDL描述,创建掩模组以用于制造硅芯片。HDL可在仿真软件上运行,并提供待生产硬件的时钟周期的准确运行状态。唯一的问题是,大部分以HDL描述的实体设计模拟器只能以几十或几百赫兹的频率运行,无法达到兆赫,甚至连千赫都很困难,对于软件程序员来说,这种频率低得几乎毫无用处。同样的HDL可用于编写可编程逻辑器(FPGA)或硬件加速器,如Mentor Graphics的Veloce。FPGA和硬件加速器可实现HDL所描述的行为,但它们的运行速度是兆赫级的。对于软件工程师来说,这一速度仍然不够,但是至少是可用的。

一旦你已经使用了存根代码和虚拟样机的全部功能,假如有一个是可用的,那么下一步就是在一个更加精确的硬件模型上验证你编写的代码,具体来说,就是RTL。开始这一步骤的最佳方法是将虚拟机(QEMU或AFM)与硬件的RTL模型结合起来,在软降仿真器或硬件加速器中运行。Mentor Graphics的产品Warpcore使这种方法成为可能。它将虚拟机与RTL执行环境进行了结合,仅在RTL被访问时才运行RTL仿真器。将虚拟机与仿真环境相结合,以几百赫兹的频率运行,看似疯狂,但是在不过度运行硬件的情况下,这种做法是可行的。如果硬件只运行一百万个时钟左右,执行效果会很好。通常情况下,仿真器更易于建立、访问和调试。一旦你需要使硬件运行超过一百万个时钟周期,则需要使用硬件加速器以实现更优良的性能。

运行虚拟机和硬件加速器的组合,或一些供应商所谓的“混合仿真(hybrid-emulation)”,可在精确硬件模型的一个时钟周期中快捷、简便地运行软件。一般这种配置的性能为100 MHz,这并不是实时的,但是其速度足以运行和调试完整的软件堆栈。

可对外围设备进行一些简单的测试,但要对驱动程序进行彻底的验证,外围设备只进行“环回(loop-back)”,还远远不够。这意味着将其与外部世界相连接,无论是通过硬件加速器上的I/O电缆,还是虚拟模型或硬件加速器相连的主机的接口。Mentor的硬件加速器系统中,将其称为co-model主机。co-model主机和硬件加速器之间快速有效的连接对于维持高水平的性能是至关重要的。

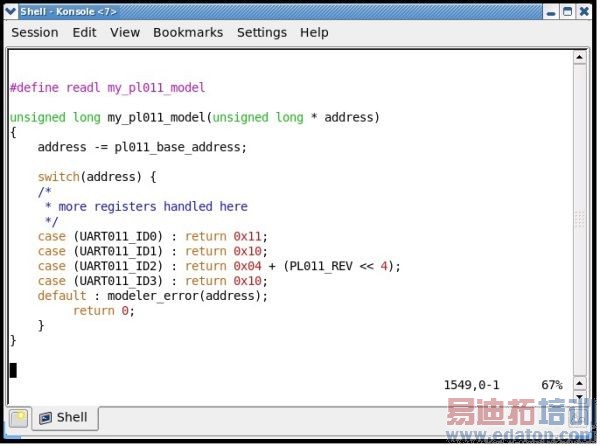

图3:重新为新驱动程序定义读/写宏指令

需要注意的是,在这个配置中完整的设计不是在RTL中。这意味着系统将正常工作,但不会表现出与最终产品相同的性能特征。从这个配置中你能看出某些方面的性能,如某些组件之间转换的流量。但是详细的性能分析则需要对系统进行更准确的表达。

当RTL代表整个设计时,你将得到整个系统一个时钟周期的准确模型。这可以用来进行详细的时间分析并得出吞吐量、延迟以及响应时间的具体数据。要使系统有效运行,你需要将其放在一个硬件加速器或FPGA原型中。一个包括实际软件的完整系统,实际上是不可能基于软件仿真进行建模的。甚至在硬件加速器平台上也只能运行于一兆赫兹。这远远超过了基于软件的仿真速度,但与实际时间相比,还是要慢得多。

上一篇:开放式FPGA增加测试灵活性

下一篇:探索复杂RF环境中的射频干扰