- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

开放式FPGA增加测试灵活性

功率放大器的输出功率必须根据每个所需的中心频率和功率电平进行调整。在调整过程中可以遵循以下步骤:

●根据待测设备的估算增益,选择一个起始VSG功率电平。

●设置VSG功率电平。

●等待VSG稳定。

●等待DUT稳定。

●使用功率计进行测量。

●如果功率在量程内,则退出。否则计算新的VSG功率电平,并返回步骤2。

调整所需的时间取决于待测设备的类型、所需的精度以及所使用的仪器类型,通常为几百毫秒到几秒。调整完成后,使用VSA进行性能测量。

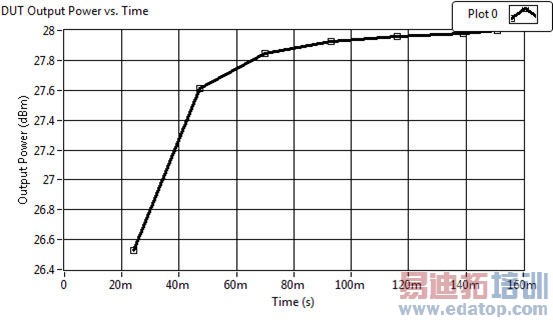

图4显示的是一个待测设备在调整过程中的输出,该设备采用传统方法来获得28dBm的平均输出功率。如果功率放大器的增益呈线性且匹配数据表中规定的标准增益,则VSG生成的第一个点会输出28dBm的功率。相反,放大器的输出只有26.5dBm,这说明功率放大器规定的标准增益并不准确。因此,需要对VSG输出功率进行调整,同时VSA捕获另一个点。此时的平均功率为27.6dBm,这表明了放大器处于增益压缩状态。总体上,该方法需要七个步骤以及大约150毫秒的时间才能使放大器的输出达到所需的级别。在这个例子中,每个步骤的待测设备稳定时间为10ms。但是,稳定时间根据每个待测设备而有所不同,这会大大影响整体的调整时间。

图4.调整功率放大器输出的传统方法显示了功率电平呈逐步增大状态。

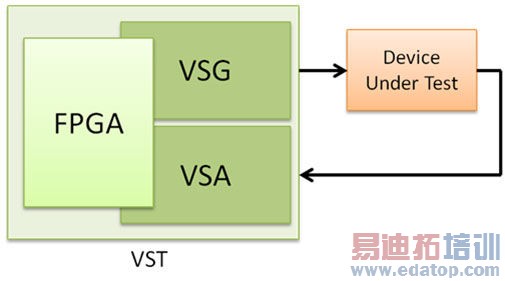

VST(矢量信号收发仪)结合了VSG、VSA和FPGA。这一组合使您可将功率调整算法的运行转移到硬件上。在图5中,虽然没有功率计,但是您也可以运行一个系统校准步骤,在VSA上获得与功率计相同的精确度。

图5. 矢量信号收发仪结合了信号发生器、信号分析仪和FPGA。

上一篇:测试混合动力发动机技术

下一篇:如何在硅芯片制作完成前进行软件开发