- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

开放式FPGA增加测试灵活性

仪器厂商早就认识到FPGA的优势,而且也利用其独特的处理能力来实现仪器的各种特性:

* 在示波器上进行预触发采集

* 在矢量信号分析仪上通过信号处理生成I和Q数据

* 实时实现模式生成和高速数字仪器的向量比较

测试设备制造商正在致力于帮助用户更好地利用FPGA,以针对更多的特定应用进行优化。为了帮助您理解这一转变的好处,以下几点是FPGA特别适用于测试应用的关键属性:

* 确定实时的处理

* 真正的并行执行

* 可重配置

* 低延迟

再进一步思考一下,您可以利用开放式FPGA来实现以前无法实现的哪些功能呢?为了说明这些可能性,以下介绍了一些利用开放式FPGA的常见测试应用。

加速测试系统

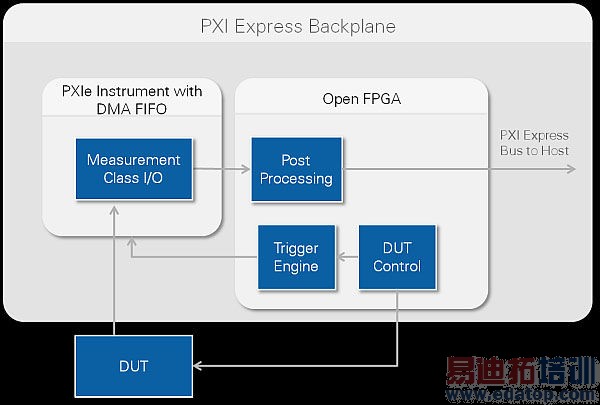

在高产量生产线的末端生产测试中,测试时间分秒必争。当生产线的测试速率与生产速率相匹配时,生产效率达到最大。如果无法实现这一匹配,则必须采用创新的技术来缩短测试时间。传统的方法通过以太网、USB或GPIB将独立的台式仪器连接到PC主机上。由于待测设备通过不同的数据总线分别进行控制、测量和处理,因而所需要的测试时间相对较长。另一种方法是使用开放式FPGA来加速该过程,如图1所示。

图1:在测试仪器中,开放式FPGA可实现触发和后处理等功能。

FPGA没有利用外部通信总线,而是使用PXIe等高速总线来连接仪器,并通过其配置端口(如I2C、SPI或其他控制总线)连接到待测设备。在此类应用中,FPGA可控制DUT(待测设备)、触发其他仪器开始采集采样数据,甚至对这些采样数据进行处理,将其转换成对主机有意义的结果。

低延迟是能够加快此类应用运行速度的一个关键因素。FPGA本身并不具有操作系统,它是在具有高速时钟速率的硬件上实现所有逻辑。这意味着一个响应可能需要一个时钟周期来进行采集、一个时钟周期来进行处理以及一个时钟周期来做出响应。如果时钟速率为200MHz(时钟周期为4ns),则一个完整的响应需要12ns。由于FPGA的确定性特性,这种响应并不是一次性的,而是每一次都是12ns。因此,FPGA就可以省去与主机相关的延迟,而且可以最小化基于主机的处理的非确定性延迟。

上一篇:测试混合动力发动机技术

下一篇:如何在硅芯片制作完成前进行软件开发