- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

28 nm时代系统设计面临的变化与挑战

IC面市以来,工艺尺度一直在不断进展。在每一新工艺代,最小特征尺寸都减小了大约三分之一,最小的晶体管占据的面积也减小了两倍。同时,数字电路的最大时钟频率在增大,功耗也在降低,其变化都相对稳定。那么,在每一新工艺代,芯片设计人员能够为系统开发人员提供新IC,集成了更多的功能,速度更快,而功耗更低。但是,这些都一去不复返了。

今天,为了减小晶体管的尺寸,工艺开发人员不得不提供给芯片设计人员涉及到速度、功耗和成本的一系列复杂条件。芯片设计人员必须采用他们所有的工具,包括新的电路设计、新体系结构方法,并对算法进行根本的修改,以便能够以相竞争的价格继续实现更好的性能,而功耗在可接受范围内。目前为止,这些方法是有效的,但是系统设计人员对此并不了解。28-nm工艺代的确是系统设计的新时代:在这一时代,系统设计人员必须理解提供硅片的芯片设计人员面临的难题及其决定。

简单尺度的结束

工艺工程师认为,基本问题在于随着晶体管尺寸的减小,互联部分越来越短,电信号特性也在不断变化。随着晶体管的减小,它们无法自动提高速度,而是开始泄漏。那么,在28 nm,设计人员看到晶体管不再像以前那样在各方面都继续提升性能,而是出现了复杂的变化。您可以简单的减小40-nm硅氮氧化物栅极晶体管的尺寸,实现相对较低的圆晶成本。但是,您既不能实现最高速率,也不能实现最低功耗。您可以通过应变工程提高速度,采用高k/金属栅极(HKMG)堆减小泄漏电流,但是增加了成本。在一定程度上,您可以通过改变工作电压来综合考虑功耗问题。您可以通过控制晶体管的阈值电压,或者设计修改,应用体偏置,牺牲速度以减小泄漏电流。但是,对于所有应用,没有一个最佳平衡点,能够以最低功耗实现速度最快的晶体管。

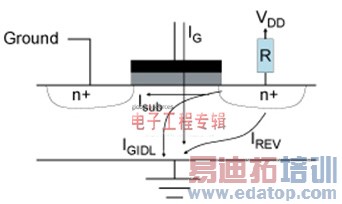

图1.晶体管泄漏源

表1.晶体管泄漏主要来源

同时,晶体管电路的最基本单元——走线,也成为一个问题。随着晶体管尺寸的减小,互联前几层的走线相应的变窄。但是,现代工艺通过充满高电阻率阻隔材料来处理这些窄沟道互联,其目的是保持铜原子多孔低k绝缘。随着工艺尺寸的减小,沟道越来越窄,但是,阻隔材料并没有变薄,因此,铜的空间更小,阻抗也就越来越大。更糟的是,在工作温度时,铜材料填充区现在靠近电子的平均自由通路,因此,铜电阻率明显增大。总体上,最底层的互联电阻增大了,进一步降低了晶体管的性能,增大了功耗。

因此,随着工艺的发展,芯片设计人员目前看到了有意思的场景——密度增大了,但是,更需要综合考虑速度、功耗和成本因素。结果是,在很多情况下,芯片设计人员发现采用新工艺技术后,速度并没有很大的提高。

下一页:IC设计的新方向