- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

满足28 nm迫切的低功耗需求

低动态功耗体系结构

除了低静态功耗,Altera Cyclone V和Arria V器件的动态功耗也较低,从而实现了最低总功耗。Altera从28LP工艺开始采用了降低动态功耗的方法,主要面向低功耗应用,包括,便携式消费类、无线链接和蜂窝基带等。TSMC阐述了提供高级工艺来实现最低总功耗而不仅仅是静态或者动态功耗的原因:

“我们之所以决定为28LPT工艺开发可靠的SiON技术,是因为无线和便携式消费类应用需求在不断变化,我们一直面对产品要符合市场需求的压力。消费者几年前需要低泄漏手持式设备,要求电池能够使用较长的时间。今天的消费者越来越依靠无线设备来浏览互联网,观看视频,听音乐,使用移动电视、GPS导航,以及传统的电话和文本服务等。主动应用功耗现在是电池使用时间的主要因素。SiON逻辑门技术由于具有较小的栅极电容,因此,动态功耗比HKMG (高K金属门)低,对于功耗受限的应用,提供的解决方案具有较低的总功耗,成本和风险也很低。”

28LP工艺具有较低的栅极电容,有源栅极电容比28HPL低30%。在Cyclone V和Arria V器件中,Altera还采用了其他方法来降低器件电容,包括用于存储器控制器的硬核IP、PCI Express,还提供收发器协议支持,减小了管芯面积及其相关电容。最后,与Stratix V器件相比,Altera还针对Cyclone V和Arria V器件的基本体系结构模块进行了优化。这些优化措施减小了硅片面积以及相关的电容,使得28LP器件系列满足了目标应用的性能要求。例如,Arria V器件逻辑阵列模块(LAB,10个自适应逻辑模块)的管芯面积比Stratix V LAB小40%。Cyclone V和Arria V器件的硬核存储器控制器也同样减小了管芯面积以及外部存储器接口的相关电容。所有减小器件电容的这些措施都降低了动态功耗,符合下面熟悉的功耗公式,其中,C表示开关电路的电容:

Altera还降低了器件收发器的动态功耗。Altera丰富的收发器设计专业知识在业界是首屈一指的,其独特的优势反映在收发器较低的动态功耗上。例如,在6 Gbps,Arria V收发器功耗不到100mW,比28-nm竞争FPGA的功耗低得多,如85℃结温,6 Gbps时每通道的收发器总功耗所示。对于采用了36个收发器Arria V器件的设计,功耗降低了5W多。

图6.85℃结温,6 Gbps时每通道的收发器总功耗

Altera在28-nm节点实现了较低的收发器功耗,这是因为我们经过了多年的磨炼,增强了专用体系结构。在可编程逻辑业界,只有我们能够持续不断的发展高级收发器技术,因此,功耗一直在逐步降低。竞争解决方案每一代产品的收发器功耗都在增加,如所示,画出了收发器物理介质附加层(PMA)功耗与多代FPGA之间的关系曲线。

图7.收发器功耗的历史发展趋势

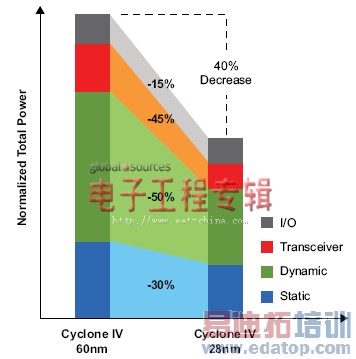

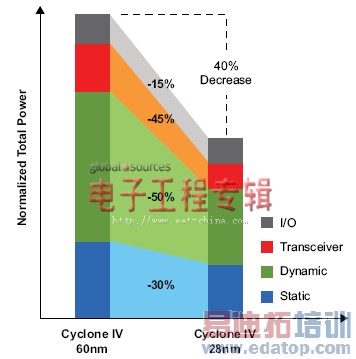

通过这些静态和动态功耗优化措施,Altera基于28LP的FPGA总功耗比前几代器件降低了40%,全面降低了功耗,如Cyclone V降低了功耗所示。

图8.Cyclone V降低了功耗

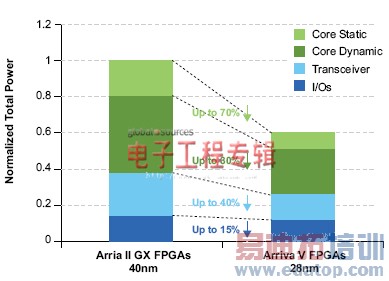

显示了Arria V器件相似的结果。

图9.Arria V降低了功耗

下一页:通过软件创新降低功耗