- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

满足28 nm迫切的低功耗需求

理想的低功耗元器件

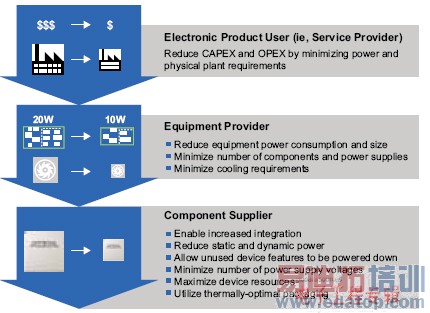

制定了这些低功耗目标后,产品开发人员必须进一步提高产品性能,同时降低能耗。而且,降低功耗还有助于帮助最终用户提高经济收益。例如,对于服务供应商依靠电子产品作为其商业模型的情况,降低功耗可以减少与电子设备供电和散热相关的运营开支。而且,降低总功耗能够降低实际供电需求。所有这些因素都有利于减小设备规模,降低投入和运营成本。如通过供应链来降低功耗需求所示,这些最终用户需求转换为设备供应商的需求,最终是元器件供应商的需求。

图3.通过供应链来降低功耗需求

FPGA和可编程逻辑器件(PLD)非常适合产品开发人员通过以下方式,以低成本来控制功耗:

●将大量的板上逻辑、存储器和处理器元件迅速集成到很少的器件中,甚至是一个器件中。

●减少支持元件和供电电源数量,减小电路板面积,降低实现复杂电子系统所需要的功耗。

●支持采用不同的实现方法和算法来精确的调整功耗。

灵活的可编程逻辑具有低功耗优势,在综合考虑全定制硅片的成本和产品及时面市时,它是非常有吸引力的选择。

在28 nm定制功耗

在28-nm节点,设计人员利用Altera器件可以针对特定的目标市场和应用来定制功耗。Altera的方法在28-nm系列产品中利用了多种半导体工艺,针对产品和某些系列体系结构进行了优化,增强了IP。结果,与前一代同类产品相比,Altera的28 nm FPGA功耗降低了40%。

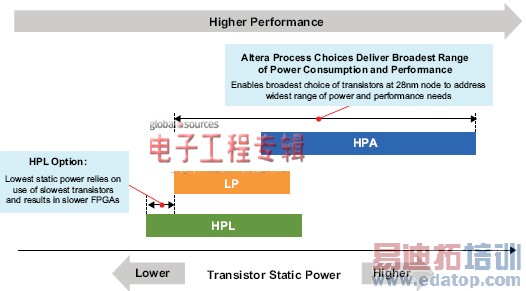

TSMC的28-nm工艺选择 显示了台积电(TSMC)的三种28-nm工艺技术,该公司是可编程逻辑供应商的28-nm节点半导体代工线。在这些工艺中,大量晶体管具有较大的静态功耗范围。左侧的晶体管静态功耗较低,而右侧的较大。这也体现了静态功耗与这些晶体管性能之间的关系。总体上,晶体管性能越好,静态功耗也就越高。Altera在28 nm产品上同时使用了28LP和28HP工艺来提高性能范围,以及多种功耗选择。第三种工艺选择是28HPL,某些晶体管的静态功耗较低,位于标以“HPL Option”的部分中,但是大量使用这类晶体管会导致FPGA运行较慢,对于很多设计人员而言是无法接受的。相应的,FPGA的28HPL工艺需要使用高速低泄漏晶体管,无法体现静态功耗的优势。

图4.TSMC的28-nm工艺选择

在28-nm节点,Altera器件是所有FPGA中总功耗最低的。这些器件之所以具有优异的功耗特性,是因为在产品开发的所有阶段都非常注重降低功耗。从28HP和28LP半导体工艺就开始重视降低功耗。

与Stratix V系列不同,Altera的其他28-nm FPGA产品——Cyclone V和Arria V系列,设计用于不需要绝对最高性能和带宽的应用。结果,它们基于28LP工艺,设计用于提供最低总功耗,如TSMC所述:

“与TSMC的40LP技术相比,基于SiON的28LP工艺采用了该系列中最低总功耗和高性价比技术,其逻辑密度将翻倍,速度提高50%,功耗降低30-50%。”

其他在28-nm节点寻求绝对最低功耗的主要半导体供应商也选择了28LP工艺,正如Qualcomm所宣称的那样:“Qualcomm与TSMC合作,推出了我们的Snapdragon S4类处理器,包括Snapdragon S4 MSM8960,它是高度集成的双核SoC,设计满足了前沿智能电话和平板电脑的低功耗需求。Snapdragon S4类处理器采用了TSMC非常复杂的28LP工艺,使Qualcomm能够突破性的实现了高性能和超低功耗的移动设备。”

在低功耗基础上,Altera还采取了其他措施来降低28LP器件的静态功耗,包括大量使用“低泄漏”晶体管等,从而降低了静态电流。此外,Cyclone V和Arria V系列还提供一些可以禁用的器件特性,包括收发器、I/O块、PCI Express模块、存储器模块以及分段式PLL等。这些特性相结合,与前一代FPGA相比,器件静态功耗降低了70%。例如,Arria V系列的器件功耗在500K LE时不到750mW,比目前的中端和高端40-nm FPGA静态功耗低得多。而竞争28-nm FPGA的静态功耗是Arria V FPGA的2.6倍。 Arria V静态功耗对比显示了Arria V GX器件的典型静态功耗,以蓝色实线表示,而以蓝色点线表示最差情况下的功耗。类似的,红色实线表示竞争中端28-nm FPGA的典型静态功耗,点线表示最差情况下的功耗。借助这些特性,在同类FPGA中,Arria V器件的静态功耗是最低的。

图5.Arria V静态功耗对比

下一页:低动态功耗体系结构