- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

最新测试技术在芯片良率提高中发挥新作用

在纳米设计时代,可制造性设计(DFM)方法在提高良率方面中已经占据了中心地位。为了实现更高的良率,人们在初始设计和制造过程本身采用了各种技术。由于采用了DFM规则,验证这些技术的有效性就至关重要。新的测试方法学重点是识别故障机制,从而提供使测量取得成功的有价值的反馈链。这些方法学使故障诊断更为有效,从而缩短良率提高周期。

过去,测试的基本目的是识别有缺陷的器件并防止它们流出制造厂。这就是制造测试和扫描测试诊断要以全新的观点进行故障和良率分析的原因。

与简单地将经测试器件分箱装入合格/失效桶的做法相比,新的诊断技术可被用于从有价值的数据中探测故障机制,最终隔离造成故障的根本原因和能够被校正的良率损失机制。在此,要采用测试技术来解决其它富有挑战性的任务,包括首次流片诊断和提高良率,这两个任务都需要有效地对无法通过测试的器件实施故障隔离。

随着大量的设计向130nm及其以下工艺转移,亚波长光罩蚀刻效应、更低的电源电压和增大的泄漏电流对良率有着重要影响。在良率低下与企业要满足市场需求之间形成了尖锐矛盾。

提高良率对企业增强赢利能力极为重要。一经发现问题区域的清晰迹象,就要开始采取正确的行动。当特征尺寸减小到130nm以下时,由于缺陷通常是不可见的,在线检查工具的效率会下降,从而使问题更加复杂。这正是测试技术需要发挥重要作用的地方。

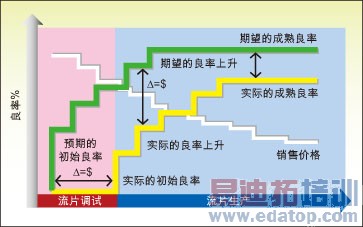

图1:在良率受到制约的纳米时代,利用DFM技术来提高初始良率固然重要;但从长远目标来看,晶圆厂具备精确预测成熟良率的能力或许更为重要。

过去20年,可测性设计(DFT)开发取得了长足进展,改进了测试质量,并降低了测试成本。最近的进展如压缩扫描测试模式及高速存储器内建自测试(MBIST)已经很快被工程师所掌握,并广泛见诸于当今的设计之中。DFT也将很快被部署用于可靠的故障分析,从而成为加快提高良率的要旨。

综合故障分析策略包括以下几个方面:用于嵌入式存储器诊断、扫描链和门逻辑的故障诊断的各种方法学。除了诊断每一个故障之外,还要将几个方面相关到到器件版图设计及最终识别实际缺陷的机制中。

识别嵌入式存储器缺陷

嵌入式存储器或许是考察故障识别过程的最佳例子,其构造的规则性使故障隔离比门逻辑要容易得多。实际上,采用针对测试算法的综合MBIST,就有可能不仅隔离特定的故障存储器单元,而且可能隔离单个晶体管。正是因为如此,存储器故障分析成为许多良率改进方案的基础。

MBIST可以全面测试嵌入式存储器的每一个例程,有时多以百计。典型的MBIST诊断引擎采用串行接口,通常利用JTAG寄存器将测试故障的准确位置及失败的算法步骤信息一起发出。该信息可以被映射到器件的物理版图以便设计工程师精确地发现缺陷的趋势。

除了测试独立的单元,测试其它存储器结构特征也很重要。针对测试这些特征的算法包括用于独立使能线、地址解码晶体管和多接口存取电路的专用测试。如果不能正确地测试嵌入式存储器的所有结构特征,那就可能留下巨大的测试质量隐患,并最终妨碍提高良率。最后,所有算法都应该进行at-speed操作以获得最高的测试质量。当然,在诊断过程中既不能对这些算法,也不能对at-speed操作进行折衷处理。

定位逻辑故障

综合故障分析策略包括用于存储器阵列和门逻辑的精确故障识别。不幸的是,许多公司对门逻辑采用有限的隔离,客户返回的除外。这就可能导致一大堆缺陷类型逃避早期的识别,因而在良率改善过程中留下巨大的隐患,从而加长了良率学习的时间,因为必需对更多的缺陷器件采样,以便确实识别缺陷的变化趋势。

不难理解为什么门逻辑故障隔离比存储器阵列要复杂得多。逻辑的随机特性不仅仅使测试生成更为困难,而且使故障隔离更为复杂。即使门逻辑诊断工具能够将故障隔离为一小块逻辑,但这对于识别特定的制造缺陷来说可能是无效的。

诊断一个未通过扫描测试的器件首先要考虑的是扫描链本身的问题。超过30%的扫描测试故障都归因于扫描链本身的问题且并不是罕见的。由于测试条件所造成的这些故障类型是令人恼怒的问题:即一个单个扫描失败可能造成整个扫描链中的结果是无效的-即使不是全部,也是绝大部分。

幸运的是诊断工具配备了针对扫描链故障的算法,这些算法工作的基础是每一个独立的扫描链通过彼此之间的逻辑相连,因此,通过分析邻近扫描链的数据,扫描链故障定位的更精确估算就可以被推断出来。

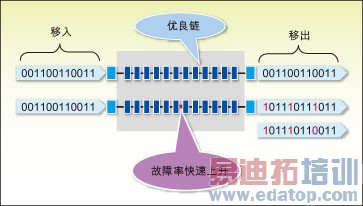

在流片诊断过程中,经常出现扫描链加载和卸载期间的时序问题(如图2所示)。对于诊断工具而言,重要的是正确地识别这些条件并精确地报告所怀疑的故障电路单元。即使采用合适功能的扫描链,精确识别引起门逻辑测试故障的征兆远非易事。曝光缺陷首先需要高质量的测试模式集。利用较大的故障模型集,如跳变和桥接,就可以获得高质量的测试模式集。

测试压缩技术增加了可能的故障类型并保持测试成本的低廉,现在130nm及以下的设计都将测试压缩技术集成到测试开发流程之中。当然,任何测试压缩方法都必须具备不增加特别的模式就能直接诊断故障的能力。这就不会增加测试负担或消除了由仅用于故障隔离的不同测试模式所引起的诊断不确定性。这样,生产故障日志就可以被诊断工具直接采用,而不必在测试设备上重新插入被测器件。

确定故障的准确逻辑位置可能是一个困难的问题。简单的粘着故障(stuck-at faults)最容易被定位。但另一方面,以某种方式可以证明,桥接缺陷本身就确实难以进行识别。在这些情况下,诊断工具可以执行一些二次计算来识别可能的疑点,并对这些疑点按照故障真实原因的可能性进行排队。利用这些结果和其它信息(如版图数据),可以证明这是一种确定器件故障根本原因的有效方法。

物理版图中的缺陷识别

把探头伸进芯片内部直接识别制造缺陷是一种成本极高的方法,它需要很昂贵的设备投资和高技能的技术人员。在开始de-processing之前,重要的是,要确保诊断工具所显示的故障逻辑网络就是某种可识别缺陷的实际位置。

图2:时序问题可能出现在扫描链的加载和卸载过程中

即使对该逻辑网络具有高度信心,要开始做de-processing通常还不够精确。许多网络很长,在继续往前布线之前应做必要的物理隔离。在版图中加亮网络可以被用于更精确地识别缺陷的位置及可能的缺陷原因。例如,如果可疑的网格被诊断工具中识别为开路,那么最好要检查过孔。或许,如果该可疑网格与另外一个网格在很长一段相邻,那么很可能存在桥接故障。进一步说,故障网络的特征可以被用作创建DFM规则的基础。

本文小结

故障分析是一个正在成长中的领域,工具越好用,收效也就越大。业界对更细微划分可疑类型的诊断工具存在持续不断的需求。这将加速首次流片的纠错。缺陷诊断的自动化使得故障分析可以在较多的样品上进行,从而缩短良率学习周期。显然,这些工具可以在缩短上市时间并改善产品质量上发挥重要作用。

上一篇:行业的代表-3458A

数字多用表

下一篇:音、视频干扰分析与抑制