- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用NI LabVIEW的并行化技术来提高测试的吞吐量

概览

二十世纪一位很有影响力的建筑设计师Frank Floyd Wright曾经说过:"每个伟大的建筑设计师都是他所处时代的伟大解读者 。"这句话同样适用于测试系统设计师们。在他们设计、开发和实现系统的时候,他们必须理解不断进步的技术,如多核处理器、现场可编程门阵列(FPGA)和高速数据总线,如PCI Express等等。通过将这些技术与NI LabVIEW并行化编程软件及NI TestStand编程管理软件结合在一起,测试工程师们可以创建出高性能的测试系统,用于并行化处理、并行化测量,甚至于在生产阶段进行完全并行化的测试。借助于基于PC机的并行化技术,用户可以将测试速度提高到传统仪器的10倍以上。

并行化处理

在传统CPU设计中,CPU性能会受限于实际的困难,如高速时钟速率带来的散热问题等。为了确保PC机平台可以满足不断增长的处理需求,芯片制造商们正在开发具有多个处理核心的新型处理器。在自动化测试应用中,为了充分发挥多核技术在性能和吞吐量上的优势,必须针对多个处理核心编写软件应用程序,即创建出在多个处理核心上分别执行的多个线程。

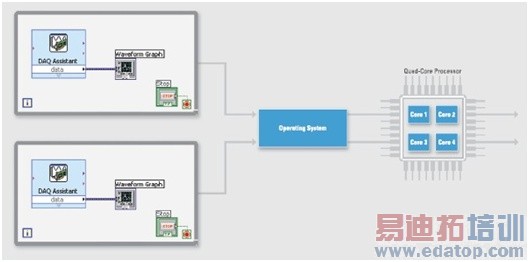

图1.LabVIEW编译器在不需要用户配置的情况下,即可为并行代码段创建独立的执行线程

利用基于文本的编程语言(如ANSI C等)编写多线程应用程序,对于多数设计和测试工程师而言,都不是一件很容易的事情,它需要精通创建和管理线程,并且懂得以线程安全的方式在线程间传递数据。利用LabVIEW图形化编程环境,工程师们可以充分发挥出多核处理的计算性能。如图1所示,在LabVIEW中,两个没有数据依赖关系的循环会自动在独立的线程中执行,而开发者不需要考虑线程管理等细节内容。如果需要了解如何利用多核处理器的应用案例,请阅读名为《使用多核处理器和NI LabVIEW来最优化自动测试应用》的白皮书。

对于特殊的数据操作和信号处理而言,为这些任务分配专用的处理单元是十分必要的。多核控制器可以很好地满足这种需求,然而对于最终的并行处理而言,它的性能很难超过FPGA。FPGA为自动化测试系统提供了无与伦比的性能和可靠性,是目前并行化编程计算硬件中的佼佼者。LabVIEW FPGA Module软件使用LabVIEW嵌入式技术对LabVIEW图形化开发进行了扩展,并且针对NI可配置I/O(RIO)硬件上的FPGA芯片。LabVIEW有着清晰的并行化和数据流表示方法,因而非常适合对FPGA进行编程。借助于LabVIEW FPGA Module软件,用户可以创建出自定义的测量和控制硬件,而无需了解低级别的硬件描述语言或板级设计。用户可以借助于个性化的并行化硬件来进行实现特殊的定时和触发例程、超高速控制、与数字协议进行接口、数字信号处理(DSP)和其它许多需要高速的硬件可靠性和确定性的应用。

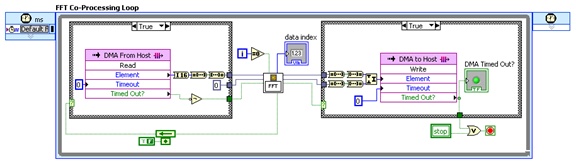

使用FPGA,用户可以实现协同处理的应用(如图2所示)。例如,使用具有新型定点计算能力的LabVIEW FPGA以及ni.com/ipnet上提供的快速傅里叶变换(FFT),用户可以在NI PXI-7852 R系列模块上的Virtex-5 LX50 FPGA中摆放40个并行化的FFT操作。随着PXI Express的专用带宽(高达1GB/秒/方向)和点对点流盘技术的出现,这种能力的价值正在不断提升。

图2.LabVIEW FPGA的定点计算能力可以使PXI FPGA上包含FFT在内的协处理应用的性能得到提高

并行化测量

并行化测量要求测试系统中所有的子部件都支持并行化的模型,而不只是处理器。其中包含了数据的采集和传输。

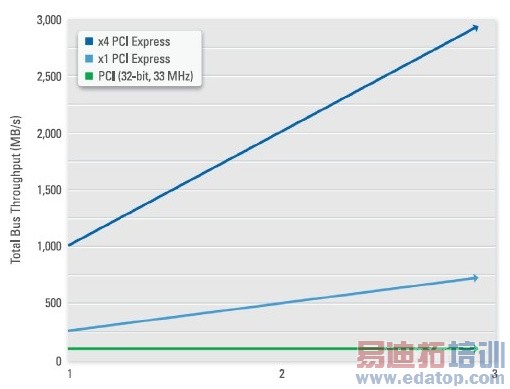

图3.PCI Express实现了专用带宽而非共享式数据传输,进而显著提高采集和传输到硬盘的数据数量

现在,模块仪器中最常用的数据传输总线包括PCI、USB、以太网和GPIB,但是它们都不支持真正的并行化数据传输模型,因为总线上的设备共享总线的带宽。如果I/O设备采集或生成的累计速率比总线可用的速率高,那么将造成数据的丢失。解决这个问题的通常办法是顺序化地进行测量,并且在I/O设备上集成大容量的板上存储器作为缓冲区,这样在等待通信总线可用的过程中,数据就不会丢失了。

相反,PCI Express是最新的高性能数据传输总线,它为每个设备提供了专用的带宽,而且提供的吞吐量比上面提到的其它商业化通信总线都要大。可用的PCI Express总线有x1、x4、x8和x16(发音为"乘1","乘4"等等)通道几种,其中每条通道的有用吞吐量为250MB/s。x1和x4选项是仪器类硬件中最为常见的,分别实现了250MB/s和1GB/s(4条250MB/s的通道)的专用带宽。

通过在背板中使用PCI Express技术,可将PXI可用的带宽从132MB/s提高到6GB/s,在带宽方面的提高达到了45倍多,同时保持了与PXI模块在软件和硬件上的兼容性。PXI Express技术与PXI平台完全整合在一起,为PXI用户提供了每个插槽1GB/秒/方向的专用带宽,以及工业上最高性能的时序和同步功能。

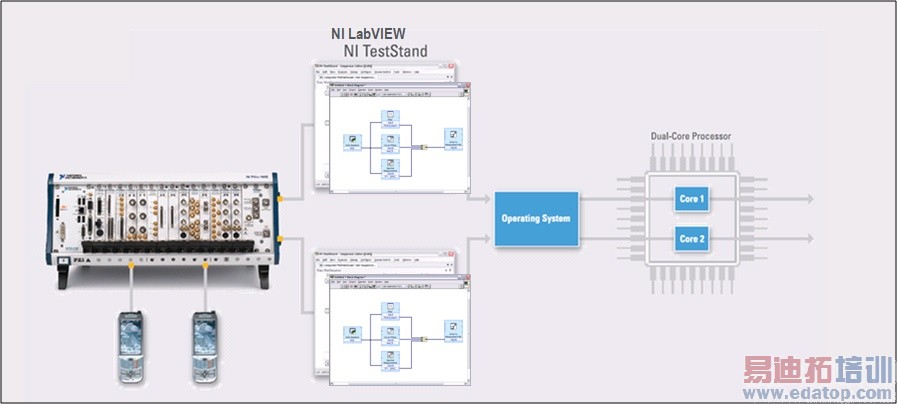

图4.PCI Express和模块化仪器为并行化测量提供了可调整的模型

在PXI Express模块采集数据时,它通过专用的PCI Express通道将数据从板上存储器写入到硬盘驱动器或者系统存储器中。当数据被传输到系统存储器中时,LabVIEW应用程序可以访问数据,而且如果与多核处理器配合使用,那么从信号到最后测量的并行化测量就实现了。

并行化测试

利用多核处理器、PCI Express总线和LabVIEW软件,用户可以创建并行化的测量系统,它们能够同时测试一个待测单元(UUT)。但是,并行化测试的定义是指多个待测单元同时接受测试。替代方案是顺序化地测试待测单元。虽然并行化测试可以显著地降低总体的测试时间、增加测试吞吐量,并且改进仪器的使用方法,但是开发并行化测试系统的复杂性是非常巨大的。开发测试管理软件以实现同时测试多个待测单元,需要理解底层的操作系统并行化工作的原理(如Windows的临界代码段)有所了解,不仅需要周密地考虑在多个待测单元间进行仪器共享,而且要避免冲突或者死锁。

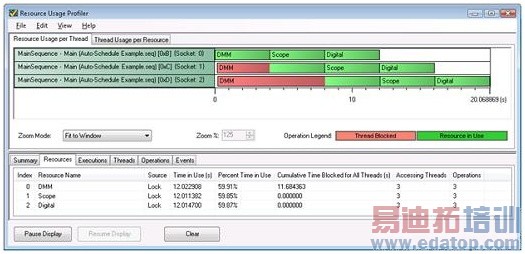

从头开发自定义的并行化测试系统的替代方案是使用即时可用的测试管理软件,如NI Teststand。该软件使用内建的特性,对并行化测试系统开发中底层的复杂度进行了抽象化,用于在多个线程中执行并行化的测试序列,同时对操作系统和仪器资源进行管理。另外,用户可以使用NI Teststand Resource Profiler工具来理解仪器的使用和并行化测试系统的执行,进而降低测试时间并提高吞吐量。Resource Profiler工具可对测试系统执行进行分析,并且确定仪器的瓶颈来帮助用户优化测试代码,区分未来仪器投资的优先顺序。如图5所示,profiler工具实时显示了仪器和其它资源的使用情况。

图5. NI TestStand Resource Profiler工具帮助开发者理解并行测试系统的执行, 进而提高了系统的吞吐量

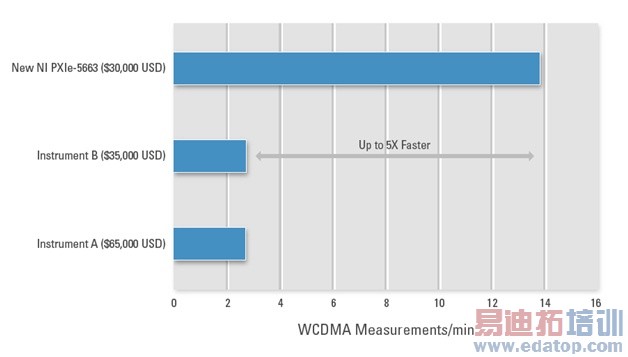

为了解释采用并行化测试构架的性能优势,请考虑比较使用PXI平台和传统仪器来实现基本的WCDMA测试序列。与W-CDMA测试标准一致,基准应该包含测量(如相邻信道功率(ACP)、占用带宽(OBW)、补偿累积分布函数(CCDF)和误差向量幅度(EVM))的时间和精度。如图6所示,在测量速度方面,基于NI TestStand、LabVIEW和PXI平台的并行化测试平台提供了5倍的改进。这可以显著地节省终端用户的开销。需要了解更多关于基准分析的信息,请查阅《射频基准比较白皮书》。

图6. 相比于传统仪器,基于LabVIEW、NI TestStand和PXI的NI并行化测试平台,提供了5倍的测量速度改进和更高的精度

完成并行测试构架

多核处理器、FPGA和PCI Express正在改变现代PC机的版图,并帮助LabVIEW图形化编程根据工程师应用逻辑的数据流向,实现真正的并行化处理和并行化测量。利用NI TestStand软件,可以完成并行化的测试构架。具有此结构的测试系统利用PCI Express提高了数据吞吐量,使用LabVIEW、多核处理器和FPGA增强了处理能力,最后利用NI TestStand软件降低了每个待测单元的总体测试时间和费用。