- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用多通道ADC使系统性能达到更先进水平

时间交织

M个ADC的时间交织可以使采样速率提高到M倍。通过合理地配置每个ADC时钟信号的相位,任何一款标准ADC IC的最大采样速率可乘以系统内ADC的数量。每个ADC所需的合适的时钟相位可以按下式计算:

![]()

M表示ADC的数量

m表示具体ADC的序号,即1≤m≤M

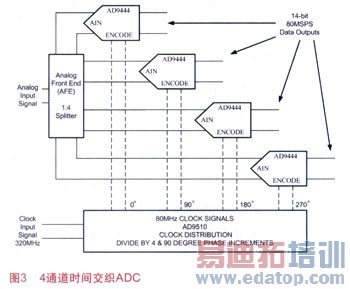

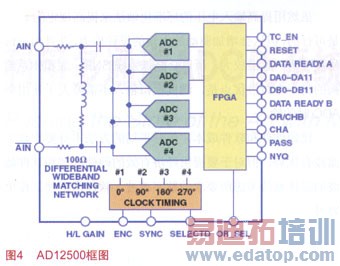

例如,一个采用AD9444 14 bit, 80 MSPS ADC组成的4通道系统,当每路时钟相位以90°(π/2)间隔适当递增时,将会产生14 bit,320 MSPS的效果。图3示出这类系统的基本框图。在AD12400/AD12500系列产品中已经采用了12 bit集成解决方案的时间交织方法。图4示出了AD12500框图,其中包括ADC、时钟管理、电源和数字后处理所有必需的功能。

增加ADC系统的采样速率最明显的好处是增加模拟采样带宽,又称作奈奎斯特频带。增加数字化仪器系统中奈奎斯特频带可以提供很多好处:数字示波器可以扩展模拟输入带宽;软件定义无线电系统可以增加信道数;雷达系统可以提高空间分辨率。图5示出14 bit,320 MSPS ADC系统对22 MHz频率信号采样的仿真FFT图。

该ADC系统的FFT频谱拥有160 MHz奈奎斯特频带。为了讨论方便,160 MHz奈奎斯特带宽被分为4个独立的40 MHz频带,每个频带代表着采样速率为80 MSPS的单个AD9444的奈奎斯特频带。22 MHz基频位于频带1。在图5可以观察到,除了基频,还可以观察到两种类型的非谐波失真分量--失调杂散和镜像杂散。对于单频输入信号引起的失真分量位置可以通过以下关系式来确定:

![]()

这些失真分量的出现是与时间交织有关的主要挑战。它们直接影响通道之间的增益、相位和失调匹配误差。实际上,这些杂散信号的幅度直接与误差幅度成正比1,2。例如,一个通道上1%的增益误差会造成52 dBc的镜像杂散幅度。当系统频率规划涉及到位于失真边带的频带时,这些杂散信号均会成为问题。在这种情况下,在开发过程中必须谨慎地管理通道之间的匹配特性。如果系统性能目标是10 bit ENOB,而且镜像杂散信号是主要因素,那么增益匹配误差必须优于0.1%,相位匹配误差必须优于0.07°(2ps @100 MHz)!为达到这个性能等级,从实现的角度考虑,必须减少或消除许多不同的误差源。

每个ADC的模拟输入和时钟输入的印制线尺寸必须匹配以保证传播时延在预算等级之内。虽然时钟电路功能很简单,但它也会引入影响系统性能的误差。与现有的ECL制造工艺相比,先进的工艺,例如硅锗RSECL(低摆幅ECL)工艺能够在信号上升、下降时和传播时延方面提供很大改进。根据输入频率,还可采取手工线路长度调整以克服孔径延时误差。

由于电源性能水平之间的差异,所以需要使用允许误差小的电源,例如靠近ADC安装的线性稳压器。另外,与温度相关的性能也需要通过机械设计保证与ADC的温度特性严格匹配。挑选ADC时还需要考虑以下一项或所有指标的匹配:增益、失调、孔径延迟和输入电容。显然,挑选四个独立的所有关键性能指标的允许误差严格匹配的ADC非常困难和昂贵!必须谨慎权衡对系统设计的开发和元件成本所增加的复杂性和风险。

采用模拟调整处理方案可以在很窄的工作条件设置下与时间交织系统中的ADC通道之间相匹配。然而采用数字后处理方法能够在很宽的工作条件设置下实现严格的通道匹配。高速、可配置数字平台,例如现场可编程门阵列(FPGA),为集成先进的后处理方法——例如AFB先进的滤波器组 ,提供了方便的工具。

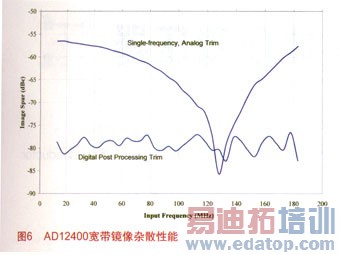

AD12400 12 bit, 400 MSPS ADC包含两个高速ADC,并且采用时间交织方法和AFB滤波器组达到采用单个民用ADC所无法实现的性能(到本文写作之日)。图6示出宽带动态性能数据,并且对模拟和数字调整方法做了比较。采用"手动调整"每个通道在128 MHz处的增益和相位可达到14bit的匹配程度(86 dBc),但性能下降得非常快:12 bit(74 dBc)性能的带宽仅为20 MHz。另一方面,采用数字调整方法,在170 MHz整个测试范围内能保持优于12 bit性能--精心设计的数字后处理方法带来的明显性能优势。

因此,当系统设计要求采样速率高于市场上可提供的单个ADC的采样速率时,考虑采用时间交织方法是很有价值的。如果在整个奈奎斯特频带内都需要保持10~12 bit性能,那么集成解决方案,例如AD12400 和AD12500,由于成功地克服了与严格通道匹配要求有关的困难而发挥了时间交织方法的优势。

上一篇:TEK工程师答疑:简化高速串行数据调试验证和一致性测试

-问答精选

下一篇:安森美半导体新的高集成度过压保护IC

减少便携设备电路板占用空间多达40%