- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

5 Gsps高速数据采集系统的设计与实现

2.4 上位机软件设计

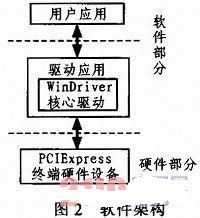

高速数据传输的上位机部分是以PC机为平台进行的软件设计。整个软件架构如图2所示,主要由用户应用程序和驱动程序两部分组成。

上位机系统通过PCI Express接口,控制板卡上的FPGA,并使上位机能够读取到FPGA以DMA方式连续上传的数据,实现上位机内存和FPGA之间数据的高速传输。该软件的驱动部分设计,依靠WinDriver的API函数和已有的PCI Express硬件设备驱动函数,完成对硬件设备的基本控制,为以后软件的进一步升级奠定良好的基础。而用户应用部分,主要是在Visual Studio环境中完成,通过调用可靠的设备驱动函数,成功地通过PCI Express接口与FPGA进行数据通信。

2.5 测试结果

1)ADC与时钟性能测试

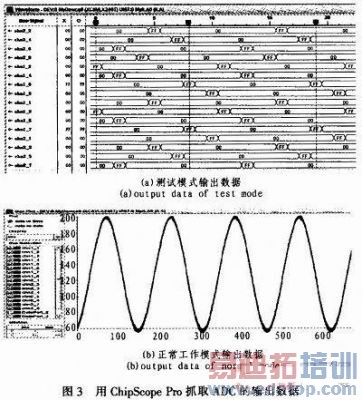

这里采用Xilinx公司ISE软件中的ChipScope Pro工具将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,直接查看ADC输出的数字信号,这些信号在操作系统速度下或接近操作系统速度下被采集,并从编程接口中引出,再将采集到的信号通过ChipScope Pro逻辑分析器进行分析。

首先让ADC工作在采样率为5 Gsps的单通道模式下,用特定的测试模式来检验ADC与FPGA之间的数据接口的准确性。将测试程序下载到FPGA并运行后,用ChipScopePro抓取ADC的输出数据如图3(a)所示。然后在单通道模式下不使用测试模式,输入2MHz的正弦信号,用ChipSco pePro抓取ADC的输出数据如图3(b)所示。

从图3(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图3(b),输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为42.9 dB,由式(2)计算得到ADC的有效位数为6.6 bit。实测表明,AD9520输出的2.5 GHz时钟以及EV8AQ160均具有较高的性能,整体指标达到设计要求。

2)上位机数据结果显示

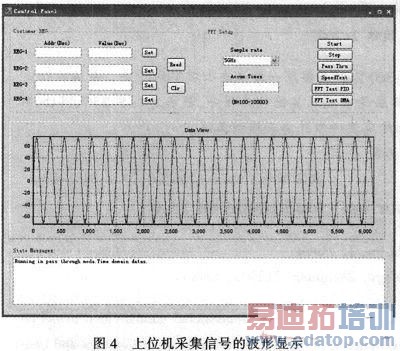

用户应用窗口程序的设计是在Visual Studio 2008环境下进行的,内部通过调用WinDriver提供的API函数及已编写的驱动函数,可以打开、查看、配置和关闭该PCI Express硬件设备。将系统配置为5 Gsps采样率的工作模式,用TeeChart画出实时采集到的波形,如图4所示,表明系统实现了数据的实时采集存储功能。

上一篇:Qualcomm

Atheros使用NI

VST进行802.11ac测试

下一篇:开发针对ECU测试的硬件在环、高速仿真与数据采集系统