- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

便携式功率分析仪设计-----频率部分电路设计

3.5频率部分电路设计

3.5.1常用测频方法微波信号的频率在微波通信、雷达、导航等微波工程中是表征微波信号特性的主要参量之一。

频率是表征周期现象的一种参数,定义为物体每秒振动的周期数,单位是赫兹(Hz)。微波电磁振荡也属于这个现象。从物理学知道,电磁振荡实质上是最简单的简谐振动。即使是非简谐振动,也可以看成是许多不同频率、相位的简谐振动之和。因此微波信号的一般表达式常写成

式中A为振幅,ω为角频率,f为频率,ψ为初相位。式(3-11)说明,表征微波信号的参数有振幅、频率和相位,就其常用者是前两个。关于振幅的测量即为功率测测量所以频率测量是功率分析中的重要组成部分。

频率测量方法目前普通采用电子计数器测量各种频率。使用电子计数器测量频率具有显示直观、操作方便以及精度较高的特点。在实际设计中主要分为硬件测频和软件测频两大类。

3.5.1.1硬件测频

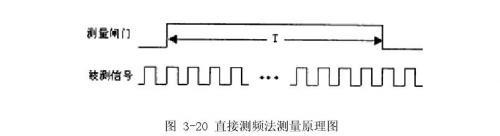

常用的硬件频率测量方法主要是直接测频法和多周期同步测频法。最简单的测量频率的方法——直接测频法如图3-20所示,就是在给定的闸门信号中填入脉冲,通过必要的记数线路,得到填充的脉冲个数,从而算出待测信号的频率。

应用直接测频法,在测量过程中,根据信号的频率大小的不同,测量方法分为两种。当被测信号频率较高时,通常选用的频率较低的一个标准频率信号作为闸门信号,而将被测信号作为填补脉冲,在固定闸门的时间内对其记数,设闸门宽度为T,记数值为n,则这种测量方法的频率测量值为:f x = n/T测量误差主要是对被测信号记数产生的±1的误差,在忽略闸门信号自身误差的情况下,测量精度为:Δfx =±1/T当被测信号频率较低时,通常选用被测信号作为闸门信号,而将频率较高的标频信号作为填充脉冲,进行记数,设计数值为N,标频信号的频率为f 0,周期为T 0。则这种测量方法的频率测量值为:

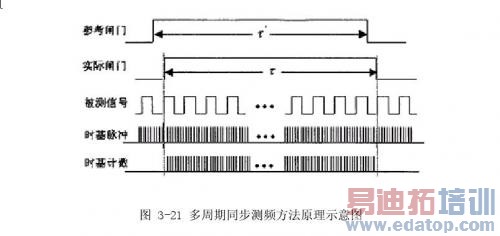

fx= f0/N在直接测频的基础上发展的多周期同步测量方法,在目前的测频系统中得到越来越多的应用,多周期同步测频记数的闸门时间不是一个固定的值,而是被测信号的整周期倍,即与被测信号同步,因此消除了对被测信号记数产生的±1个的误差,测量精度大大提高,而且达到了在整个测量频段的等精度测量,多周期同步测频方法原理如图3-21所示。

首先,给出闸门开启信号,此时,计数器并不开始记数,而是等到被测信号的上升沿到来时,才真正开始记数,然后,两组计数器分别对被测信号和时基脉冲记数,当闸门关闭时,计数器并不立即停止记数,而是等到被测信号上升沿到来的时候才真正结束记数,完成一次测量过程,可以看出,实际闸门与被设定的闸门并不严格相等,但最大差值不会超过被测信号一个周期,设对被测信号的记数值为Nx,对时基信号的记数值为N0,时基信号的频率为f0,闸门时间为τ,则被测信号的频率为:

3.5.1.2软件测频

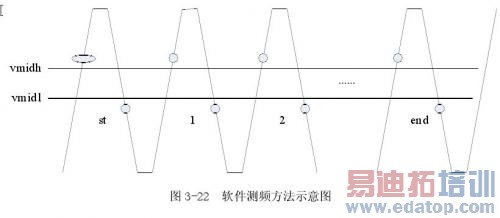

软件测频,所选择的触发窗口的宽度和波形幅度相关,在此我们定为波形幅度的10%,计算在某一段波形穿过触发窗口的个数,然后计算出波形的周期和频率,在图3-22中,令vmidh=VPP/2+5%*VPP, vmidl=VPP/2-5%*VPP,从数据区首地址开始找大于vmidh的点,找到点后,再找小于vmidl的点,把这一点的位置赋给start,找大于vmidh的点,再找小于vmidl的点,令per_num=1.依次类推,每次找到大于vmidh的点,再找到小于vmidl的点per_num++,这样在数据区找到的最后大于vmidh的点,再找到小于vmidl的点位置赋给end,那么per_num就是找到的周期个数,根据时基以及start和end的值,就可以计算出周期。

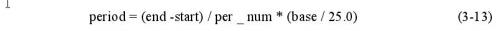

周期计算公式如下:

其中base代表时基,由于时基是固定的,所以点与点之间的时间是固定,所以可以通过起始点和结束点的位置(采样点的序号),确定数量的周期个数计算波形的周期。测出了被测信号的周期,然后将该时间的倒数作为频率来进行频率测量,使用公式:f =1/T其准确度取决于周期的测量精度。用此种方法计算周期数对于超过选择窗口的毛刺等尖峰会误认为一个周期,也不准确;对于类似

周期波形也无法准确判断其周期个数。波形时间类参数的计算,是和时基密切相关的。

所以根据以上分析,我们采用多周期同步测量方法。

3.5.2方案设计

频率计数器主要测量射频载波(CW)信号的频率,为整机提供频率测量数据。频率测量信道的主要设计思路是:预分频-整形-计数。射频信号通过前端功分器进入频率测量模块,由于功分器输出在-60~+20dBm范围内,我们通过集成数控增益射频微波放大器,以及限幅二极管调整信号满足后级预分频器输入信号电平要求。预分频部分的作用就是将高频或射频段的信号通过固定的分频比例,将其转换为中低频信号,便于后端频率计数器利用其计算信号频率。

3.5.3预分频模块设计

在频率测量模块中,由于计数部分是由FPGA实现,而整形电路现在的分频器往往都将其集成在其中,所以分频器的选择直接影响频率测量模块的性能。由于根据系统设计指标输入频率范围要求10MHz~6GHz,常用高分频比的微波分频器不能满足如此高频率输入信号的要求;同时在保证分频精度的前提下,工作频率在3GHz以上的微波分频器一般都采用1:2、1:4或1:8的较低的分频系数。所以设计采用2级分频方法,将分频器级联以满足对输入信号在3GHz以上信号频率的测量。

一级分频器采用HJ-DYF104,分频比为1:4的微波分频器,工作频率范围10MHz~8GHz,输入电平范围-12~+12dBm,输出电平范围-3±1dBm,其设计还具有以下特点:

1)单片芯片混合微组装工艺集成;

2)系列化设计,内置耦合及电流退耦电容,在设计中可以直接接入微波信号,不需要再进行信号耦合;

3)其输入输出端均50电阻匹配,这一特点也为分频器的级联提供便利;

4)标准全密封金属外壳封装,封闭式封装很大程度减小了微波信号对后级信号传输的干扰;

5)满足军用环境工作条件:工作温度范围:-55℃~+85℃,存储温度范围:-65℃~+125℃。符合系统设计总体要求。

由于实行分频器级联,所以两级分频器之间阻抗匹配以及输入输出电平转换,将直接影响分频器的工作质量。

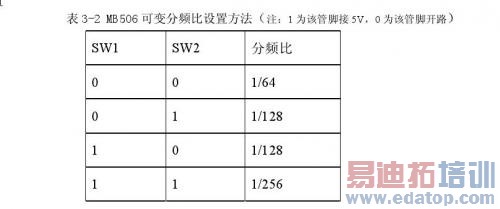

所以设计中二级分频器选用了MB506.芯片输入信号幅值-4~5.5dbm,一级分频器HJ-DYF104输出电平范围满足MB506的输入要求;并且MB506输入阻抗为50,这使得两级分频器间的连接变得十分简单。这个芯片最大输入频率支持2.4GHz.功耗较低90mW,工作环境温度要求不高-40℃~85℃,价格低廉,并且芯片内部集成放大,整形电路。其应用电路极为简单,在设计中就可以直接省去整形电路。其输出为1.6V峰峰值的ECL电平,只需要经过简单的电平转换就可以直接送入FPGA实现频率测量功能。芯片设计有64、128、256三种分频比,通过改变其SW1、SW2脚的接法,可得到不同分频比。

该芯片被现在市场上许多民用频率计所采用,通用性好。并且MB506自带整形功能且为ECL标准输出电平,所以只需要在后端加入简单的电平转换电路,获得满足TTL电平的方波信号即可直接送入FPGA进行计数,也简化了电路。

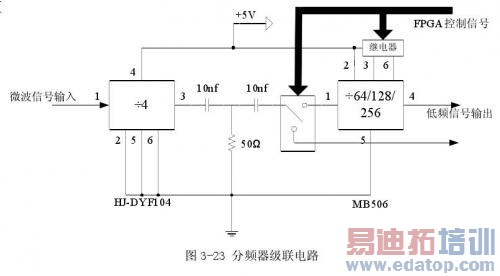

如图3-23所示,按图中连接方式,实现可变分频比的,射频级的载波信号(10MHz~6GHz)分频功能。而我们频率测量的方法既是通过多周期同步测量方法测量得到分频后中低频信号频率f s,则实际输入信号频率fo为:

其中N为分频比例。那么由于多周期同步测量方法频率计数误差是一个分频后的信号时钟周期,因此当送入分频器的信号频率较低时,如果采用固定128或者256等更高的分频比例,就会造成频率测量误差的增大。所以采用FPGA控制分频比例,当信号频率在10MHz~100MHz范围时,如上图所示,通过控制单刀双掷开关,让信号经4分频后就直接送入后段,这样通过控制动态改变分频比例,实现更高精度的频率测量。

上一篇:基于NI

PXI

Express平台的石油管复合挤毁试验机控制

与数据采集系统搭建

下一篇:便携式功率分析仪设计----功率分析仪软件设计