- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DIY手持多用示波表,系统解决方案,软硬件实现

三、方案设计

3.1 系统功能实现原理(除图片外需有文字介绍)

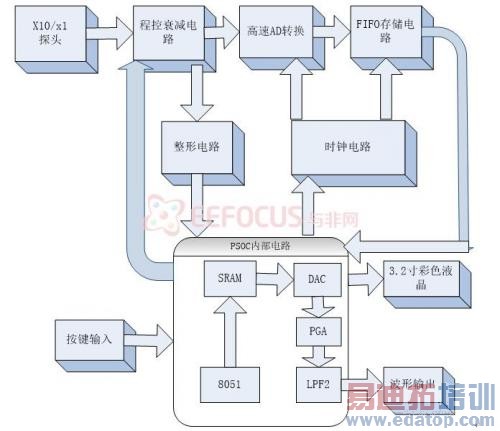

系统硬件结构框图

下面就各个模块电路做以简单介绍

1.程控放大电路和电源电路:

将程控放大电路与电源电路放在一块讲,是因为他们有着密切的联系。

程控放大器的作用是对输入信号进行衰减或放大调整,使输出信号电压在AD转换器输入电压要求范围内,达到最好的测量与观察效果,所以程控放大器电路在规定带宽内的增益一定要平坦,故对运算放大器的要求比较高,在本电路中我选用的是NSC公司生产的高速运算放大器LM6172双运放,带宽为100MHz,转换速率3000v/μs,每通道消耗电流2.3mA,输出电流可达50mA,完全满足本电路的要求,选择该芯片的另一个原因是价格,邮购价格为8元一片,相比ADI,MAX等公司几十元一片的高速运放芯片来说算是很廉价了,电源采用正负双电源供电,由于整个电路总的电源输入为单8v,所以专门用一片dc/dc电路MC34063为其构成了负压转换器再经稳压得到-5v电压,+5v通过对输入电压稳压得到。

2. 高速AD转换与FIFO存储电路

数字示波器中最重要的电路是AD转换电路,它的作用是将被测信号采样并转换成数字信号存入存储器,说它是数字示波器的咽喉一点也不为过,因为它直接决定着数字示波器所能测量的最高频率,根据乃奎斯特定理,采样频率至少是被测信号最高频率的2倍才能复现出被测信号。而在数字示波器中采样频率至少应该是被测信号频率的5~8倍才行,否则根本观察不到信号的波形。在本电路中我选用的AD转换芯片为BB公司的8位高速AD转换器ADS830E,官方资料给出的采样频率为10kSa/s~60MSa/s, 通过实验发现转换速率在1K以下工作也很正常,所以本示波器的最低采样频率为600Sa/s,要说明的一点是高速AD转换器一般都有高低端转换速率的限制,比如TLC5540,8位AD转换器,转换速率为5MSa/s~40MSa/s,我试过当转换频率降到2M以下时就不能正常工作,所以选择AD转换芯片时不仅要注意最高转换速率还要关注最低转换速率,否则可能导致电路无法正常工作。有朋友也许会问8位转换精度会不会有点太低?其实8位转换器对于示波器来说是够用的,就拿这个电路来说,我选用的LCD显示模块的分辨率为320*240,垂直分辨率为240格,而8为转换精度的分辨率为256格,比显示器的分辨率还高,所以绝对够用。还有就是价格及电路的设计,在最高采样率相同的情况下10位AD转换芯片的价格是8位AD转换芯片的几倍,而且位数的增加也使电路的复杂程度大大增加,将直接影响处理速度,导致屏幕刷新过慢,反而影响性能。所以本着够用的原则本示波器选用60M的8位AD转换芯片ADS830E。

3. 时钟产生电路

时钟产生电路为AD转换器提供一系列的采样时钟信号,分别为600Hz、6kHz、60kHz、600kHz、3MHz、6MHz、30MHz和60MHz,共8种,分别对应着不同的水平水平扫速。

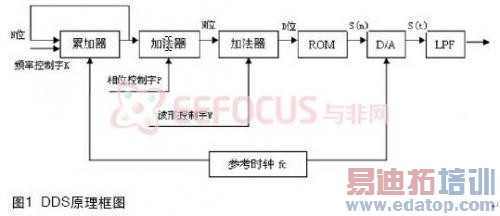

4.信号发生原理DDS介绍

DDS是从相位概念出发直接合成所需波形的一种频率合成技术。一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器(LPF)构成。

DDS的原理框图如图1所示。其中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P、波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位幅度码S(n)经D/A转换器变成阶梯波形S(t),再经LPF平滑后就可以得到合成的信号波形。合成的信号波形的形状取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。DDS系统中除了D/A转换和低通滤波电路外都是数字电路,以往的设计都基于纯数字芯片设计,很难实现单芯片的解决方案,而PSoC的出现刚好满足了这种单芯片、全集成的要求。

上一篇:《讲述.电子人》:深圳让我的青春躁动不安

下一篇:光纤测试阶段常见问题解析