- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

湿度环境下关于薄膜电阻的稳定性测试

这些事实包含了很多开放式问题:

。为什么测试温度仅仅增加45K,偏置湿度的影响会这么大?

。为什么薄膜电阻对偏置湿度的反应比干热更敏感?

。为什么更高的电压会导致更低的漂移?

。在偏置湿度测试中,降级的加速机制是什么?

。是否有合适的方法,能够估计和预测经过偏置湿度应力后的阻值漂移?

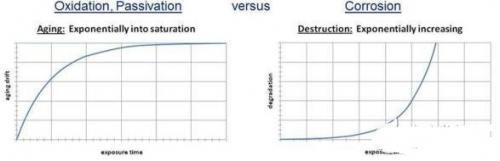

最初的85/85测试被设计成可以加速湿气渗透进非密封的IC封装,以便引发金属层里的腐蚀失效。在评估测试结果的时候,应当始终搞清楚,测试结果是由(可预测)的老化过程还是由(破坏性)的降级造成的。这样我们就可以彻底地区分氧化/钝化效应和腐蚀机制。图2显示了由这两种原因引起参数漂移的基本区别。

图2:氧化/钝化与腐蚀机制

3.深入研究的测试程序

我们的测试计划通盘考虑了下面这些因素:

。按照AEC-Q200(同一批次,对所有被测变体进行激光微调)的要求,使用认证过的灵敏的薄膜电阻阻值;

。比较偏置湿度85 / 85测试结果与40 / 93测试结果;

。引入70℃/90% RH和90℃/40% RH这两个中间测试状态;

。延长测试或暴露时间到4000小时(10000小时);

。使用两种不同的电绝缘漆;

。在每个变体上施加两种电压/负载(从额定电压的10%到30%,利用偏置湿度测试,按照标准车用元器件的要求进行认证);

。比较偏置测试和HAST 130(高加速应力测试:130℃和85%RH偏置湿度测试,相同的批次和电气状态)的结果。

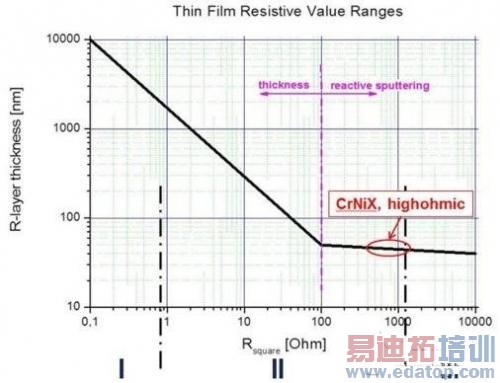

很重要的一点是,两种漆都按照85 / 85(也就是说我们只按照行业标准对可用的样品进行了基本的研究)的行业要求经过了完整的认证和发布。另一个重点是必须从最灵敏的阻值范围内选取样品。图3显示了薄膜电子设计的临界边缘,可做借鉴。

图3:不同阻值的电阻层厚度

方形电阻R□的整个阻值范围使有三种合金(I,II和III)决定的。合金II采用的是CrNiX(X代表第三种元素)。1Ω~100Ω之间的R□是通过改变2μm到30nm的电阻层厚度来实现的。在氧化和腐蚀同时发生时,电阻层的改变会引发不同的效应。较厚的电阻层会出现表面或颗粒边界效应。相反,我们必须面对在薄电阻层上出现的体积效应,这种效应可以影响整个层的厚度。在氧化的情况下,所有电阻材料都会受到影响。在腐蚀的情况下,这会导致电阻层的彻底破坏。为了做试验,我们挑选了这类敏感的样品,保证样品会出现最坏的情况(电阻类型有MINI-MELF,MMA0204,最大阻值为180 kΩ,R□大约是800Ω)。

各个测量点是从20个测试样品的单一结果得到的。为了实现统计覆盖到全部事件(最坏情况)的98%,每个测试点的参数值的概率分布都进行了估值。

4.测试结果和主要发现

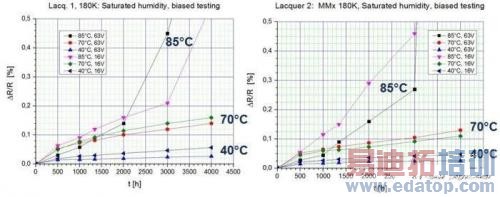

两种不同电绝缘漆和两个不同偏置电压的测试结果见图4.我们找到了两个明显的降级机理,可以区分老化(40 / 93,70 / 90)和破坏性的腐蚀状态(85 / 85)。

图4:在测试环境中暴露4000小时后的测试结果(40 / 93,70 / 90,85 / 85)

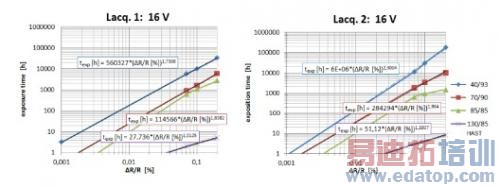

在这个阶段,还不能根据85 / 85测试数据做比较或预测。因此,为了使用可比较的数据,我们在0.07%到0.1%再到0.2%的ΔR / R低漂移水平上,提出了对所有阻值漂移进行标准化的方法。通过定义一个既明显但又几乎不会造成破坏的可接受且在标准要求内的漂移水平,我们就可以比较全部测试数据,另外还可以加上HAST 130的测试结果。标准化参数漂移的结果(在我们这个例子是ΔR / R)与相应的暴露时间参见图5.暴露时间的标准化的各个测量点要么是直接推导出来的,或是经过我们不同的湿度测试,从120个独立的ΔR / R漂移测量结果推算出来的。

图5:在非破坏性的ΔR / R水平上对测试结果进行标准化

上一篇:8种噪声测试技术的实现,包括模块电源、MOSFET等

下一篇:LabWindows/CVI虚拟仪器设计技术基本控件使用之:三态开关