- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于正交矢量放大的MRS信号采集模块设计---- 采集模块硬件设计(二)

录入:edatop.com 点击:

4.3锁相环电路

4.3.1倍频电路设计思路

CPLD的FLASH中存储的正弦波的一个周期用256个点来输出,而正弦波的频率要求是在1300Hz~3000Hz范围内可调,步长为0.1Hz.这就要求FLASH模块的时钟频率在333KHz~768KHz范围内按步长25.6Hz可调。CPLD用的外部晶振为125MHz,如果这个时钟频率由CPLD分频产生,不能达到设计要求。但是CPLD可以实现频率在1300Hz~3000Hz范围内按步长0.1Hz可调,再把这个频率进行256倍频就可以达到设计要求了。

4.3.2锁相环电路芯片选择

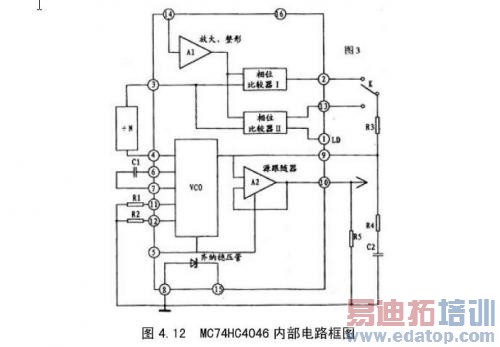

利用锁相环可以实现非常稳定的倍频电路。锁相环是一个相位负反馈的闭合环路,其频率跟踪原理图如图4.10所示.

锁相环是由相位比较器(也称鉴相器)、低通滤波器LPF和压控振荡器VCO三个环路部件组成的一个反馈控制系统。相位比较器(也称鉴相器)对基准输入信号和压控振荡器引入的信号进行比较,当基准信号和压控振荡器信号频率与相位相同时,鉴相器的输出为零;当两信号的频率和相位不同时,鉴相器的输出就产生一个误差电压,这个误差电压经过滤波环节,控制压控振荡器,使其输出频率和相位与输入信号的频率和相位绝对匹配,锁相环路既实现了"锁相"。

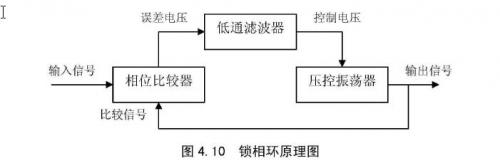

将压控振荡器输出信号经过N分频后再输入到相位比较器中,那么锁相环锁定后压控振荡器输出的信号频率就是基准信号频率的N倍,这就是锁相环实现倍频电路的原理,如图4.11所示。

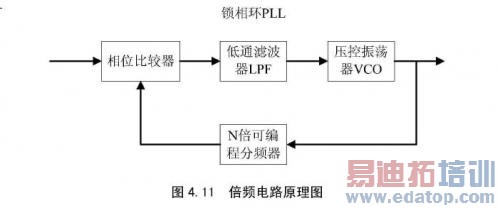

现在常使用集成电路锁相环74HC4046,它的内部电路框图如图4.12所示。