- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

工业运动控制中的测量技术

高性能示例:控制级接地,检测选项C、D或E

在本例中,需要进行人员安全隔离。检测选项C、D和E均有可能。在所有三个选项中,选项E提供最优质的电流反馈,并且作为高性能系统,系统中可能存在FPGA或其他形式的处理,可提供适用于隔离调制器信号的数字滤波器。对于选项C的ADC选择,通常采用分立式隔离传感器(很可能是闭环HE),以实现比使用当前嵌入式ADC产品更高的性能。与共模放大器相比,该配置中的选项D为隔离式放大器,因为需要进行安全隔离。隔离式放大器会使性能受限,因此嵌入式ADC解决方案便可满足需要。与选项C或E相比,该选项可提供保真度最低的电流反馈。此外,虽然可将嵌入式ADC视为"免费",将隔离式放大器视为"廉价",但实施时通常还需要额外的组件进行偏移补偿和电平转换,以进行ADC输入范围匹配,从而提高了信号链的总体成本。

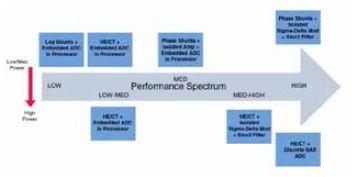

在电机控制设计中,可采用许多拓扑检测电机电流,并需考虑多种因素,例如成本、功率水平以及性能水平。大多数系统设计人员的重要目标是改善电流检测反馈,以在其成本目标范围内提高效率。对于较高端的应用,电流反馈不仅对于效率,而且对于其他系统性能测量(如动态响应、噪声或转矩波动)也至关重要。很显然,在各种可用的拓扑中,存在性能由低到高的连续体,图5为粗略映射图,展示了低功率和高功率选项。

图5.电流检测拓扑性能图谱

电机控制系统设计人员目标、需求以及发展趋势:从HE传感器转换至分流电阻

与隔离式-调制器耦合的分流电阻可提供最优质的电流反馈,其中,电流电平足够低,完全可满足分流需求。目前,系统设计人员的明显倾向于从HE传感器转换至分流电阻,并且与隔离式放大器方案相比,设计人员还倾向于采用隔离式调制器方案。仅仅更换传感器本身就可降低物料清单(BOM)和PCB装配成本并提高传感器的精度。分流电阻对磁场或机械振动均不敏感。将HE传感器替换为分流电阻的系统设计人员往往会选择隔离式放大器,并继续使用之前在基于HE传感器的设计中使用的ADC来限制信号链中的电平变化。然而,如前所述,无论ADC性能如何,该性能都将受到隔离式放大器性能的限制。

而且进一步将隔离式放大器和ADC替换为隔离式-调制器可消除性能瓶颈,并大大改善设计,通常可将其从9到10位的优质反馈提升到12位。此外,还可配置处理-调制器输出所需的数字滤波器,以实现快速OCP环路,从而消除模拟过流保护(OCP)电路。因此,任何BOM分析不仅应包括隔离式放大器、原始ADC、两者之间的信号调理,而且还应包括可消除的OCP设备。AD701A隔离式-调制器基于ADI公司的iCoupler技术,具有±250 mV(通常用于OCP的±320 mV满量程)的差分输入范围,特别适合阻性分流器测量,是扩大此趋势的理想产品选择。模拟调制器对模拟输入持续取样,而输入信息则以数据流密度的形式包含在数字输出流内,其数据速率最高可达20 MHz.通过适当的数字滤波器(通常为适用于精密电流测量的Sinc3滤波器)可重构原始信息。由于可在转换性能和带宽或滤波器群延迟之间作出权衡,因此更简略、更快的滤波器能够以2μs的数量级提供快速OCP响应,非常适用于IGBT保护。

对缩小分流电阻尺寸的需求

从信号测量方面来看,目前的一些主要难题与选择分流电阻有关,因为需要实现灵敏度和功耗之间的平衡。大阻值将确保使用调制器的整个或尽量大的模拟输入范围,从而获得最大的动态范围。但是,由于电阻会出现I2×R的损耗,因此,大阻值还会导致电压下降和效率降低。电阻自身的发热效应而导致的非线性情况也会是使用较大电阻所面临的挑战。因此,系统设计人员面临着左右权衡取舍以及进一步恶化的后果,他们往往需要选择一个适当大小的分流电阻,以满足不同电流电平下各种型号和电机的需求。如果面对数倍于电机额定电流的峰值电流,并需要可靠捕获两者的值,则保持动态范围也是一个难题。控制系统开机峰值电流的能力会因设计不同而有很大差异,从额定电流以上浮动诸如30%的严格控制,到高达10倍于额定电流的系数。加速以及负载或扭矩变化也会产生峰值电流。但是,系统中的峰值电流通常处于驱动器设计额定电流的4倍范围内。

面对这些难题,系统设计人员正在寻找具有更宽动态范围或具有更高信噪比和信纳比(SINAD)的高性能-调制器。最新的隔离式-调制器产品具有16位分辨率并可确保高达12位有效位数(ENOB)的性能。

SINAD =(6.02 N + 1.76)dB,其中N = ENOB

顺应在低功耗驱动器中使用分流电阻的趋势,电机驱动器制造商出于性能和成本方面的考虑,也在设法提高可利用该拓扑的驱动器的额定功率。唯一可行的方法就是使用阻值更小的分流电阻,而这需要引进性能更高的调制器内核,以辨识减弱的信号幅度。

系统设计人员(尤其是伺服设计人员)仍在不断探索,试图通过缩短模数转换时间,或者通过采用与隔离型-调制器和分流电阻拓扑有关的数字滤波器降低群延迟的方式提高系统响应。如前所述,可在转换性能和带宽或滤波器群延迟之间作出权衡。更简略、更快的滤波器可提供更快的响应,但会降低性能。系统设计人员分析滤波器波长或抽取比的效果,然后根据其终端应用需求作出权衡。提高调制器的时钟速率会有所帮助,但是许多设计人员已实现在AD7401A支持的20 MHz最高时钟速率下操作。提高时钟速率的一个缺点就是辐射电位和干扰(EMI)效应。在相同的时钟速率下,性能较高的调制器可改善群延迟与性能之间存在的权衡关系,从而在性能影响较小的情况下实现更快的响应时间。

上一篇:基于正交矢量放大的MRS信号采集模块设计----核磁共振信号采集模块的原理及分析

下一篇:高阻器件低频噪声测试技术与应用研究--用于聚合物钽电容的漏电流噪声研究