- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

安捷伦S系列示波器硬件设计解剖

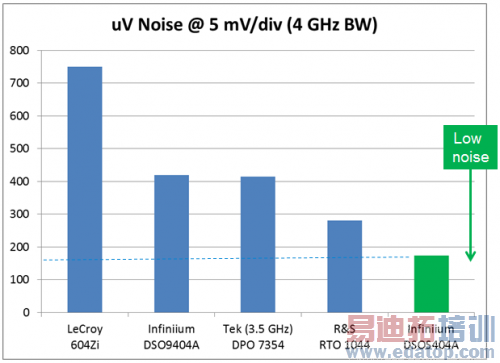

以业界常见的4GHz带宽示波器为例,低噪声对比如下图8所示。

图8

3. 校验滤波处理

个人认为图1中S系列示波器捕获板圈起来的"新的校验滤波处理FPGA"的位置是错的(这个图是来自美国研发部门),这个FPGA应该与以前示波器一样, 在ADC后面,执行内存管理,校验滤波处理,显示刷新加速处理等功能。现在多了一个FPGA,应该未来有更广泛的用途,比如:执行FFT运算,抖动测量运 算,函数运算,DDC运算等(只是猜想)。不论如何,S系列示波器更注重使用硬件FPGA进行复杂运算。

按照技术手册上给的说明,现在这些数字信号处理功能包括:硬件加速显示处理(在深内存时,加快缩放时波形更新的速度);频响校验滤波处理;示波器内部可控 的带宽限制滤波器(从500MHz带宽到示波器带宽);支持1-3通道和2-4通道的差分处理;执行去嵌入处理(包括:InfiniiSim,精密探头, 均衡)。

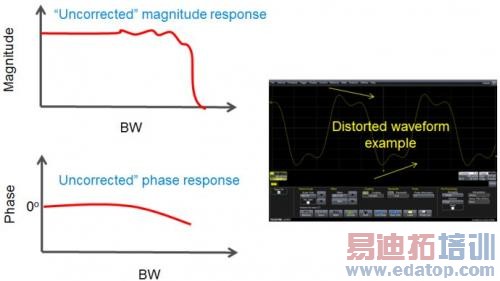

频响校验滤波是非常重要的,下面做个简要说明。图9-1中是正常的硬件的频响,包括幅度响应和相位响应,硬件设计没法做到理想化。直接使用存硬件对信号的影响可由右边图看出来,会导致波形的失真(相位响应更易产生这样的结果)。

图9-1

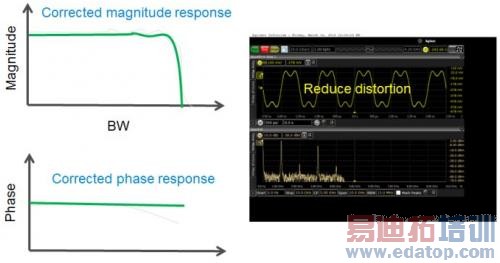

通过执行校验滤波器,使得幅度响应和相位响应达到比较理想化的状态,相应波形失真较小,比较好的显示出了原始波形(如9-2的右边图所示)。

图9-2

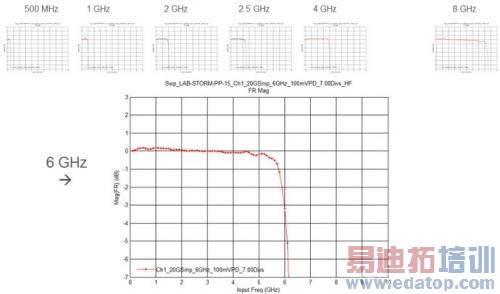

S系列示波器各种型号校验后的频响如图10所示,都达到了比较好的平坦响应的状态。

图10

上一篇:浅析多通道隔离示波器在浮动测量中的应用

下一篇:示波器探头基础入门指南(下)