- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

UHF RFID读写器编解码模块的FPGA实现

引言

UHF RFID读写器具有读写距离远、读写速度快等优点,已成功运用于供应链管理、航空管理和后勤管理等诸多领域。本设计依据的协议是EPC C1G2(EPCClassl Generation2)。

本文介绍了一种读写器的编解码部分由FPGA来完成的设计方案,由FPGA负责前向链路的PIE编码和后向链路的FM0/miller解码,且解码模块可对标签突发传来的数据立即检测并实施解码,实现了较快的解码速率。FPGA选用的是Altera公司的EP1C3T100C6芯片。

1、RFID系统介绍

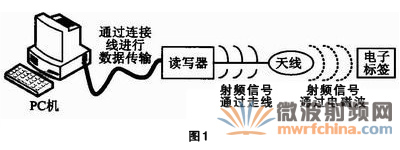

图1所示为RFID系统,主要由PC机、读写器、天线和电子标签组成。读写器与电子标签之间的数据通过天线进行传递。读写器作为RFID系统的一部分,既能与标签通信,又能向PC机传输数据并执行上位机所要求的操作,具有发送、接收和处理数据的能力。读写器系统按其所处理信号的不同,主要由2个部分组成,即处理数字信号的基带部分和处理模拟信号的射频部分。

图1 RFID系统

2、EPC C1G2协议的相关介绍

EPC C1G2标准具有如下特点:速度快,速率可达40~640 kbps;可以同时读取标签的数量多,理论上能读到1000多个标签;可在密集的读写器环境下工作,能迅速使用变化无常的标签群;存储区域多,可延伸使用用户的内存需求;功能强,具有多种写保护方式,安全性强;通用性强,符合EPC规则;产品价格低,兼容性好。

2.1 PIE编码介绍

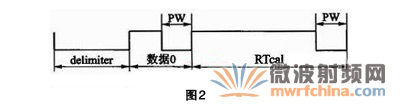

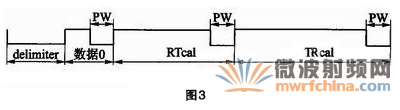

EPC C1G2协议规定发送链路(即读写器向标签发送数据)采用的编码方式是脉冲间隔编码(即PIE编码)。读写器每次给标签发送命令,都以帧同步码或前同步码开始所有的通信。帧同步码格式如图2所示,帧同步码由delimiter、数据0和RTcal三部分组成。前同步码格式如图3所示,前同步码由delimiter、数据0、RTcal和TRcal四部分组成,除delimiter外,各部分均以低脉冲PW结尾,且各部分PW的长度必须相同。de limiter的长度固定为12.5μs,协议规定允许有±5%的误差。delimiter用于给电子标签校准时钟。

图2 PIE编码的0和1

图3 PIE前同步码

前同步码只用于表明盘存周期开始的Query命令中,其他命令则以帧同步码开始。当Query命令数据中的DR=1、前同步码中的TRcal长度为33.3μs时,可设定反向链路(即标签向读写器发送数据)频率最高为640kHz。

2.2 FM0和miller码介绍

Query命令中M参数值决定了标签返回数据的编码方式,即FM0、miller2、miller4、miller8四种。FM0码在每个数据边界处和数据0中间反相。miller码则是在两个连续的数据0的边界处和数据1的中间反相。miller编码序列每位可包含2、4、8个副载波周期,即miller2、mille r4、miller8三种编码形式。这四种编码方式都以各自特定的帧头开始,而具体选择哪种帧头,则由Query命令中Trext参数值决定,并且在结尾处都有一位"dummyl"作为数据传送的结束标志。

2.3 读写器与标签通信流程

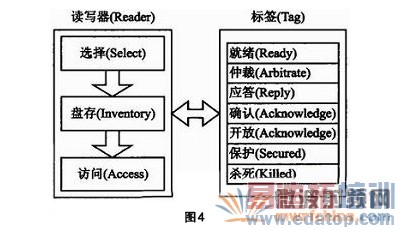

EPC C1G2协议规定读写器的命令分为选择、盘存、访问3类,而标签的工作状态分为就绪、仲裁、应答、确认、开放、保护、杀死7个状态,读写器命令类型和标签状态如图4所示。读写器依赖3类命令通过改变标签所处的状态,实现对标签群的筛选,以及对单个标签的识别和访问过程。读写器与标签的通信过程略一编者注。

图4 读写器命令类型和标签状态

3、总体设计

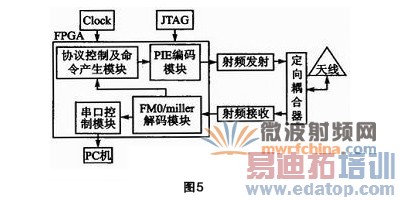

在本读写器设计中,ARM与FPGA协同工作。ARM芯片是LPC2148,工作时钟是20 MHz,主要完成对读写器系统的控制。而FPGA则负责编解码部分的数据流处理,工作时钟频率是25 MHz。图5是FPGA部分的整体设计框图。

图5 整体设计框图

FPGA中的模块主要包括协议控制及命令产生模块、PIE编码模块、FM0/miller解码模块,以及用于与PC机交互的串口控制模块。

工作过程如下:对读写器命令数据及其相应的CRC5/16校验位进行PIE编码,编码完成送到射频发射端,数字信号通过控制射频芯片RF2 173的开关引脚实现调制深度为100%的OOK(On-Off Keying)调制,并经由收发分离的定向耦合器,通过天线发射出去。

场内标签接收到读写器发送的信息后,在允许其通信的情况下,会根据读写器发送来的命令参数,选择4种编码方式中的一种,将要回复读写器的数据进行编码,经调制之后在空间传输。

读写器天线接收到标签信息后,经由定向耦合器将标签信息送到读写器的射频接收模块,该模块对标签信息进行解调,并将解调后得到的数字信号送给FPGA的FM0/miller解码模块。解码模块根据数据的编码方式选择相应的电路解码,解码后的数据返回给协议控制及命令产生模块。该模块根据上次发送的命令以及接收到的标签信息作出判断,产生下一次的操作命令数据,发给PIE编码模块,与该标签进行进一步的信息交互或选择重新读取另外的标签。

同时,为了准确获取标签信息,必须将读写器与PC机相连。读写器通过由FPGA实现的串口模块与PC机相连,对读取到的标签信息做必要的显示,如标签返回的RN16、EPC、UII等。

4、FPGA实现电路

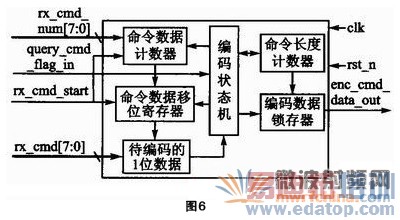

为了实现FPGA部分的功能,在Altera公司的EP1C3T100C6芯片上,利用Quartus II软件进行设计,PIE编码模块设计如图6所示。

图6 PIE编码模块设计框图

4.1 编码模块设计

PIE编码由pie_encode模块实现。该模块接收命令产生模块并行发来的8位数据,按照协议规定及设置,先给命令数据添加特定的帧头,并根据数据传输速率,对命令数据及其CRC5/16校验位进行PIE编码,编码完成后输出给射频发射模块调制,然后通过天线发送出去。其设计框图如图6所示。

PIE编码模块由编码状态机作为控制模块。状态机的状态由命令帧头和数据0和1组成,即idle、delimiter、tari、rtcal、trcal、data_ sendl、data_send0 7个状态,其中idle是空闲状态,接收到开始信号后跳转到其他状态。状态机的流程按照命令的组成依次进行,每个状态按照协议要求保持特定的时间,直至命令编码完成。由于Query命令和其他命令的帧头不同,query_cmd_flag_in信号用于指示此次发送来的数据是否为Query命令数据,如果是,则在编码时加入TRcal命令段;否则,跳过TRcal状态。

在接收部分数据开始发送指示信号rx_cmd_start与要发送的数据rx_cmd、rx_cmd_num保持同步,编码模块中的命令数据计数器和命令数据移位寄存器根据rx_cmd_start信号将8位数据并行送入各自的寄存器。

接收完成后,数据寄存器会根据计数器中的值进行相应的移位,将无效数据移出,保证有效数据是从命令寄存器中的最高位开始。同时,每完成一位数据的编码,计数器自减1,移位寄存器也自动左移一位,将下一个要编码的数据放入待编码数据寄存器中,该寄存器由此去控制状态机的下一个流程。

发送部分主要由一个命令长度计数器组成,该计数器根据命令参数的设置以及所处的状态进行计数,控制状态机在某个状态保持的时间当一位数据编码完成,计数器清0,并开始对下一位数据计数,同时状态机也跳转到下一个状态,而编码数据则根据状态机的状态以及计数器的值拉高或拉低,并由锁存器将编码后的命令锁存输出。这样就实现了边编码边调制的目的,提升了命令发送的速率,也节省了硬件资源。

4.2 解码模块设计

解码部分由data_pre_process、fm_and_miller_decode、data_post_decode 3个模块组成。data_pre_process是解码数据预处理模块,接收射频模块解调后的数据。因为射频发射和接收使用的是同一根天线,发射的数据信息以及其他杂波信号经常会泄露进解码模块。该模块主要是去除信号中的毛刺,并对接收数据的高低电平长度进行判断,看是否符合编码规则,如果均在合适的范围内,则视为成功。同时产生待解码数据的采样信号,以及其他指示信号,以便解码模块的数据处理;若不符合要求则丢弃这部分数据,重新检查分析新来的数据信息。

data_post_process是解码数据确认及串并转换模块。解调后的数据经过了解码预处理模块的初步判断,只是符合了一定的编码规则,在解码过程中还可能会出现诸如帧头出错、结尾数据不为1等其他错误。该模块通过判断解码模块的error和data_success信号,确认此次解码是否成功,若成功,将接收解码数据,同时考虑到串行数据传输速度较慢,本模块会对解码数据进行串并转换,然后8位并行地将解码后的数据传输给其他模块。

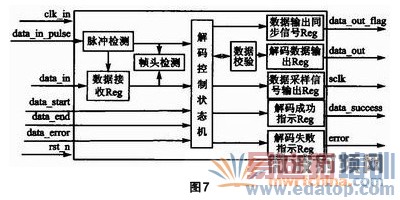

fm_and_miller_decode是解码模块。其组成框图如图7所示。

图7 miller2 解码结构图

该解码模块主要由解码状态机控制。状态机的状态由初始态、数据解码态,以及最后的解码成功和解码失败状态组成。接收到解码开始信号时,状态机由初始态跳转到数据解码态开始解码,在解码过程中,如果发现输入的数据违背了编码规则或不符合命令的设置,则直接跳入失败状态。在该状态下,会有一个解码失败信号error产生并输出。如果解码顺利进行到结束,则跳转到解码成功状态,会有一个解码成功信号data_success产生并输出,控制下一个模块的工作。这样解码状态机一边接收待解码数据,进行解码处理,一边将前面处理完的数据输出给CRC5/16校验模块,实现了类似于流水线的工作,节省了解码时间。

解码模块接收部分通过采样信号接收待解码数据,这样便只需检测采样信号,节省了计数器的消耗。采样到的数据首先进行帧头检测,判断使用的帧头类型及编码形式,若帧头检测正确,则实施去帧头处理,将有效数据通过控制状态机流程来进行解码。而其他控制信号,即来自解码预处理模块的数据开始传输指示data_start,数据传输结束指示data_end,数据传输错误指示data_error则直接控制状态机状态的转换。

解码完成之后,根据前面发送命令的类型,对解码后的数据进行CRC5/16校验,若校验正确,则去掉校验位,将有效数据输出;若错误,则返回给状态机,发出解码错误指示。同时,根据状态机所处的特定状态,在每一个解码数据期间会输出持续一个周期的数据采样信号sclk,以及在数据开始解码时便与解码数据同步输出的信号data_out_flag,以便后续模块进行数据的采样与控制。

5、软件仿真与硬件测试

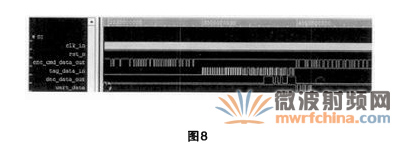

以上各模块均使用硬件描述语言实现。在Quartus II9.0中全部编译通过,满足时序要求,编译报告显示本设计共消耗了679个LE资源。调用Modelsim软件仿真验证。使用了Quartus II软件的Signaltap逻辑分析仪,捕捉了读写器实际工作时FPGA的编解码数据。

图8是读写器先后发送不同命令并与标签交互的部分流程。图9是读写器发送的Query命令的PIE编码,所发送的命令数据是1000_00110000 0000010101,其中前4位1000为Query命令的命令码,后面18位则为命令数据。

图8 命令发送流程及标签信息的返回

图9 命令的PIE编码

图10是读写器接收到标签返回的miller2编码信息后的操作。为了便于观察,将解码后的数据也作为一路信号显示,即decode_data。最后一路信号是串口要发送的数据。图10中的enc_cmd_data_out信号是读写器接收到标签返回来的信息后,发出的ACK命令,发送的命令数据为01_0001111010100111,其中前两位01为ACK命令的命令码,后面的16位数据按照协议要求为标签返回的RN16。

图10 命令的miller2解码

图11 Signaltap的采样信号

图11是在读写器工作时利用Signaltap逻辑分析仪捕获到的解码后的标签数据及采样信号。

结语

本文介绍了在EPCC1G2协议下,利用FPGA快速处理大量数据流的优势,实现UHF RFID读写器中编解码模块的设计方案,解决了读写器读取标签速率难以提升的问题。经过软件仿真与实际硬件测试,读写器工作良好,速度、性能均得到显著提升。

来源:电子科技大学作者:于志宏,张红雨