- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种 SAW RFID 阅读器的信号处理电路设计

录入:edatop.com 点击:

0 引言

RFID(Radio Frequency Identification)技术由于优秀的识别性能而被认为是二十一世纪最有应用潜力的十大技术之一,它可以应用到工业生产、国防军事、日常生活等社会的各个方面。在我国,倡导科技奥运的北京奥运会在门票、地铁、食品安全管理中已被试用。基于SAW(Surface Acoustic Wave)标签的RFID系统采用了先进微电子加工技术制造的SAW器件,具有体积小、重量轻、批量成本低、可靠性高、识别距离远、多功能等优点,与基于IC标签的RFID系统有很好的互补性,尤其在基于IC标签的RFID系统应用于带有金属物体、高温、强电磁干扰等恶劣环境无能为力时,基于SAW标签的RFID系统就显示了它的优越性,同时SAW标签也适甩干压力、加速度、温度等参数的测量,此技术在欧美已得到一定的应用。在我国,此方面的研究近几年才开始展开,技术还不够成熟。本文将介绍一种SAW RFID阅读器的信号处理电路设计及其软件设计。

1 阅读器的系统分析

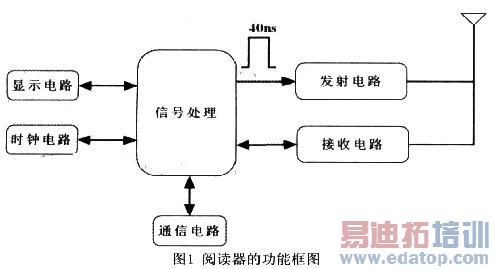

阅读器采用模块化设计,最基本单元的为射频电路与信号处理电路。如图1所示,射频系统包括发射电路与接收电路,信号处理电路包括信号处理单元与外围电路。根据功能需求, 增加相应的电路,包括有通信电路、显示电路、存储电路、时钟电路等外围电路。

阅读器工作开始后信号处理电路产生一段脉宽为40ns脉冲控制信号,送给发射电路,经过发射电路一系列调制处理,转换成脉宽是40ns,载频是915MHz的射频询问信号,通过天线发射出去。遇到SAW标签后,标签反射回带有标签信息的射频回波信号,阅读器接收时经过接收电路一系列处理,解调出代表标签信息的回波包络信号,回波包络信号是具有24位,脉宽40ns的脉冲回波,每个回波的延迟时间约为115ns。之后送给信号处理电路进行进一步的识别和处理,完成识别标签的信息。

2 信号处理电路设计

信号处理电路主要负责阅读器的系统控制与信号处理任务。包括:发射时,控制射频开关截取40ns脉冲信号;接收时,数字采集经过射频接收电路解调的回波信号,将回波信号转化为标签编码数据进一步处理。其中回波信号的每个脉冲的脉宽为40ns,每个脉冲信号延迟时间为115ns,带宽则为 接收处理过程就是高速数据采集过程。分析指标要求,信号处理电路设计的关键点如下:

接收处理过程就是高速数据采集过程。分析指标要求,信号处理电路设计的关键点如下:

(1)产生高速控制信号控制发射端的射频开关在40ns开与断。

(2)模拟信号到数字信号的转换速度。

(3)经过高速模数转换后,采样速率很快,信号处理器接收数据的速度必须匹配ADC(Analog To DigitalConverter)的转换速度。

对于关键点(1),选择高速处理器,通过软件编程实现40ns响应时间的高速控制信号。

对于关键点(2),模拟信号的最高频率达到

根据奈奎斯特采样定律,采样频率要在64MHz以上,本系统采用采样频率为80MHz的高速ADC。

对于关键点(3),ADC采样速率很高,达到80MHz,处理器无法直接接收处理如此庞大的采样数据。所以需要数据缓冲,这里选用FIFO(First Input First Output)实现数据缓存功能。

2.1 系统结构与器件选择

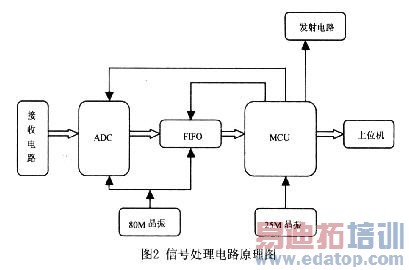

为了使系统结构简单,我们选用一种高性能的MCU(Micro Controller Unit)作为系统的信号处理核心。如图2所示,信号处理电路由MCU、ADC、FIFO、以及其他外围电路组成。

FIFO的选择:FIFO接收存储来自ADC高速输出的数字信号,还要将数据输出给MCU,这对FIFO的存取速度由很高的要求,这里选用IDT公司的SUPERSYNC II系列FIFOIDT72V223,最高166MHz操作时钟,容量1024x9 bit,具有可编程性,选用异步模式。

MCU的选择:通过软件编程实现40ns的脉冲控制信号,接收时实现高速的数据采集,RFID系统要求高速工作速度,这里选用性能优秀C8051F131。C8051F是完全集成的混合信号系统级芯片,它的CIP-51内核采用流水线结构,在同频率下是标准8051指令执行速度的12倍,C8051F131最高支持100MHz的时钟频率,处理速度也可达到100MIPS,32个I/0,128K Flash,8448字节内部RAM,可寻址64KB的片上外部RAM。

时钟的选择:ADC与FIFO的工作状态由MCU控制。钟振提供ADC采样时钟与FIFO写时钟,ADC采样时钟与FIFO写时钟只有同步数据才能不丢失,通过查询器件的数据资料,ADC转换速度与FIFO的存取速度可以实现衔接,可共用钟振。FIFO的读时钟与控制由MCU产生。

2.2 硬件电路设计

根据系统结构与器件的数据资料,部分电路设计如下:

(1)AD9057的电路设计:将射频接收电路输出端接入AD9057输入端:AD9057的8位数字信号输出端与IDT72V223的低8位输入端连接;使用C8051F13l控制AD9057的PWRDN端,控制AD9057的工作状态。

(2)IDT72V223的电路设计:在IDT72V223主复位过程中,对相应引脚置位可确定其工作模式。选用异步、标准IDT工作模式;数据输入由WCLK和WEN控制,输入时钟与输出时钟完全独立;只要REN和WEN使能,就可以读写数据;OE为低,表示允许输出端输出;此外,IDT72V223也提供了丰富的状态信号,将IDT72V223低8位输出端连接C8051F131的I/O口。

(3)通信电路、显示电路、时钟电路、电源电路等其它电路的设计,按照器件数据资料的要求完成电路连接。

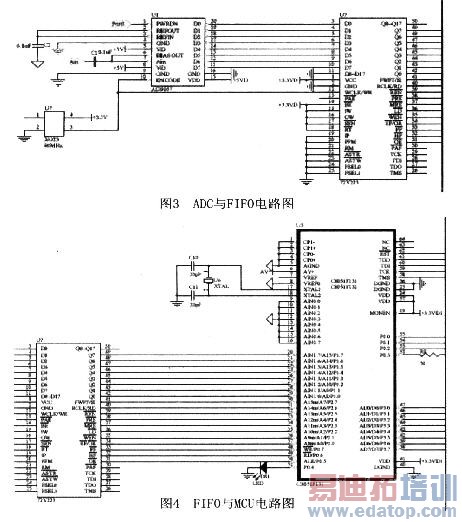

利用Protel DXP绘制电路图与PCB版图,部分电路如图3和图4所示。完善器件布局,仿真电路与电气检查,完成加工制作。

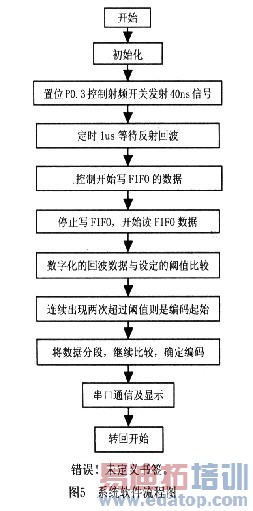

系统软件流程如图5所示,系统开始工作,通过MCU初始化ADC与FIFO的工作状态,产生40ns脉冲询问信号控制射频开关,经过1us识别标签的传播延迟,MCU控制ADC采样与FIFO的写操作,待模数转换完成后,将FIFO数据写入MCU,并与参考阈值比较,从而确定回波信号的编码信息,最后通过串口上传至上位机及显示,实现进一步处理。

4 结论

本文介绍了SAW RFID阅读器的信号处理电路设计与软件设计过程,通过实验表明,采用FIFO作为ADC与MCU之间的桥梁,起到很好的数据缓冲作用,降低了对MCU性能的要求,基于C8051F131设计的RFID阅读器的信号处理电路,具有结构简单,成本低,容易实现等特点。

RFID(Radio Frequency Identification)技术由于优秀的识别性能而被认为是二十一世纪最有应用潜力的十大技术之一,它可以应用到工业生产、国防军事、日常生活等社会的各个方面。在我国,倡导科技奥运的北京奥运会在门票、地铁、食品安全管理中已被试用。基于SAW(Surface Acoustic Wave)标签的RFID系统采用了先进微电子加工技术制造的SAW器件,具有体积小、重量轻、批量成本低、可靠性高、识别距离远、多功能等优点,与基于IC标签的RFID系统有很好的互补性,尤其在基于IC标签的RFID系统应用于带有金属物体、高温、强电磁干扰等恶劣环境无能为力时,基于SAW标签的RFID系统就显示了它的优越性,同时SAW标签也适甩干压力、加速度、温度等参数的测量,此技术在欧美已得到一定的应用。在我国,此方面的研究近几年才开始展开,技术还不够成熟。本文将介绍一种SAW RFID阅读器的信号处理电路设计及其软件设计。

1 阅读器的系统分析

阅读器采用模块化设计,最基本单元的为射频电路与信号处理电路。如图1所示,射频系统包括发射电路与接收电路,信号处理电路包括信号处理单元与外围电路。根据功能需求, 增加相应的电路,包括有通信电路、显示电路、存储电路、时钟电路等外围电路。

阅读器工作开始后信号处理电路产生一段脉宽为40ns脉冲控制信号,送给发射电路,经过发射电路一系列调制处理,转换成脉宽是40ns,载频是915MHz的射频询问信号,通过天线发射出去。遇到SAW标签后,标签反射回带有标签信息的射频回波信号,阅读器接收时经过接收电路一系列处理,解调出代表标签信息的回波包络信号,回波包络信号是具有24位,脉宽40ns的脉冲回波,每个回波的延迟时间约为115ns。之后送给信号处理电路进行进一步的识别和处理,完成识别标签的信息。

2 信号处理电路设计

信号处理电路主要负责阅读器的系统控制与信号处理任务。包括:发射时,控制射频开关截取40ns脉冲信号;接收时,数字采集经过射频接收电路解调的回波信号,将回波信号转化为标签编码数据进一步处理。其中回波信号的每个脉冲的脉宽为40ns,每个脉冲信号延迟时间为115ns,带宽则为

接收处理过程就是高速数据采集过程。分析指标要求,信号处理电路设计的关键点如下:

接收处理过程就是高速数据采集过程。分析指标要求,信号处理电路设计的关键点如下: (1)产生高速控制信号控制发射端的射频开关在40ns开与断。

(2)模拟信号到数字信号的转换速度。

(3)经过高速模数转换后,采样速率很快,信号处理器接收数据的速度必须匹配ADC(Analog To DigitalConverter)的转换速度。

对于关键点(1),选择高速处理器,通过软件编程实现40ns响应时间的高速控制信号。

对于关键点(2),模拟信号的最高频率达到

根据奈奎斯特采样定律,采样频率要在64MHz以上,本系统采用采样频率为80MHz的高速ADC。

对于关键点(3),ADC采样速率很高,达到80MHz,处理器无法直接接收处理如此庞大的采样数据。所以需要数据缓冲,这里选用FIFO(First Input First Output)实现数据缓存功能。

2.1 系统结构与器件选择

为了使系统结构简单,我们选用一种高性能的MCU(Micro Controller Unit)作为系统的信号处理核心。如图2所示,信号处理电路由MCU、ADC、FIFO、以及其他外围电路组成。

FIFO的选择:FIFO接收存储来自ADC高速输出的数字信号,还要将数据输出给MCU,这对FIFO的存取速度由很高的要求,这里选用IDT公司的SUPERSYNC II系列FIFOIDT72V223,最高166MHz操作时钟,容量1024x9 bit,具有可编程性,选用异步模式。

MCU的选择:通过软件编程实现40ns的脉冲控制信号,接收时实现高速的数据采集,RFID系统要求高速工作速度,这里选用性能优秀C8051F131。C8051F是完全集成的混合信号系统级芯片,它的CIP-51内核采用流水线结构,在同频率下是标准8051指令执行速度的12倍,C8051F131最高支持100MHz的时钟频率,处理速度也可达到100MIPS,32个I/0,128K Flash,8448字节内部RAM,可寻址64KB的片上外部RAM。

时钟的选择:ADC与FIFO的工作状态由MCU控制。钟振提供ADC采样时钟与FIFO写时钟,ADC采样时钟与FIFO写时钟只有同步数据才能不丢失,通过查询器件的数据资料,ADC转换速度与FIFO的存取速度可以实现衔接,可共用钟振。FIFO的读时钟与控制由MCU产生。

2.2 硬件电路设计

根据系统结构与器件的数据资料,部分电路设计如下:

(1)AD9057的电路设计:将射频接收电路输出端接入AD9057输入端:AD9057的8位数字信号输出端与IDT72V223的低8位输入端连接;使用C8051F13l控制AD9057的PWRDN端,控制AD9057的工作状态。

(2)IDT72V223的电路设计:在IDT72V223主复位过程中,对相应引脚置位可确定其工作模式。选用异步、标准IDT工作模式;数据输入由WCLK和WEN控制,输入时钟与输出时钟完全独立;只要REN和WEN使能,就可以读写数据;OE为低,表示允许输出端输出;此外,IDT72V223也提供了丰富的状态信号,将IDT72V223低8位输出端连接C8051F131的I/O口。

(3)通信电路、显示电路、时钟电路、电源电路等其它电路的设计,按照器件数据资料的要求完成电路连接。

利用Protel DXP绘制电路图与PCB版图,部分电路如图3和图4所示。完善器件布局,仿真电路与电气检查,完成加工制作。

系统软件流程如图5所示,系统开始工作,通过MCU初始化ADC与FIFO的工作状态,产生40ns脉冲询问信号控制射频开关,经过1us识别标签的传播延迟,MCU控制ADC采样与FIFO的写操作,待模数转换完成后,将FIFO数据写入MCU,并与参考阈值比较,从而确定回波信号的编码信息,最后通过串口上传至上位机及显示,实现进一步处理。

4 结论

本文介绍了SAW RFID阅读器的信号处理电路设计与软件设计过程,通过实验表明,采用FIFO作为ADC与MCU之间的桥梁,起到很好的数据缓冲作用,降低了对MCU性能的要求,基于C8051F131设计的RFID阅读器的信号处理电路,具有结构简单,成本低,容易实现等特点。