- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

RFID晶片的攻击技术分析及安全设计策略

录入:edatop.com 点击:

本文以采用磁耦合和CMOS制程的RFID产品为例,简要介绍了此类晶片的构成,在列举各种破坏性/非破坏性攻击方法的基础上,从软/硬体角度分析现有的各种安全措施如何在设计阶段应对这些攻击,或使攻击变得难以实施,以及如何避免不良的设计。

以前,人们普遍认为由于采用了各种复杂的认证演算法、密钥等来保护数据免受未获授权使用,IC卡具有磁卡无法比拟的安全性能。但在90年代中期,大部份的IC卡处理器都被成功地实施了逆向工程,因此这个看法有了很大的改变。除了采用更新的设计技术以外,更重要的是在IC卡晶片设计与实现过程中考虑抗攻击措施,以保护重要的数据不被非法使用。

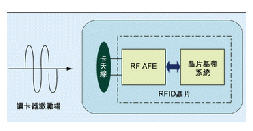

从结构上讲,RFID是一个包含射频类比前端(RF AFE)和基频讯号处理两大部份的单片积体电路(见图1)。基频系统包括控制逻辑(甚至微处理器)和必要的记忆体,AFE部份是RFID的能量与讯号介面,提供片上基频系统工作所需的电源和时脉等辅助讯号,完成数据的接收与发送功能。由于RF AFE屏蔽了智慧卡片上的电源、时脉、上电复位(POR)等讯号与外界的联系,在一定程度上减少了攻击实施的点,与接触式智慧卡相较在安全性方面有一定的提升。

智慧卡晶片攻击技术及应对措施

根据是否破坏智慧卡晶片的实体封装可以将智慧卡的攻击技术分为两大类:破坏性攻击和非破坏性攻击。

破坏性攻击和晶片逆向工程在最初的步骤上是一致的:使用发烟硝酸去除包裹晶片的环氧树脂;用丙酮/去离子水/异丙醇完成清洗;氢氟酸超声浴进一步去除晶片的各层金属。在去除晶片封装之后,透过金丝键合恢复晶片功能焊盘与外界的电气连接,最后可以使用手动微探针获取感兴趣的讯号。对于深次微米以下的CMOS产品,通常具有3层以上的金属连线,为了解晶片的内部结构,可能要逐层去除以获得重构晶片版图设计所需的资讯。在了解内部讯号走线的基础上,聚焦离子束(FIB)修补技术甚至适用于将感兴趣的讯号连到晶片的表面供进一步观察。

非破坏性攻击主要针对具有微处理器的产品,其方法主要包括软体攻击、窃听技术和故障产生技术。软体攻击使用微处理器的通用通讯介面,寻求安全协议、加密演算法以及他们实体实现的弱点;窃听技术采用高时域精密度的方法,分析电源介面在微处理器正常工作过程中产生的各种电磁辐射的类比特征;故障产生技术藉由产生异常的应用环境条件,使处理器产生故障,因而获得额外的存取途径。

智慧卡的攻击一般从破坏性的反向工程开始,其结论可以用于开发廉价和快速的非破坏性攻击方法,这是最常见的最有效的智慧卡攻击模式之一。

1.破坏性攻击及其防范

a.版图重构

破坏性攻击的一个重要步骤是重构目标晶片的版图。透过研究连接模式和追踪金属连线穿越可见模组(如ROM、RAM、EEPROM、ALU、指令译码器等)的边界,可以迅速识别晶片上的一些基本结构,如数据线和地址线。

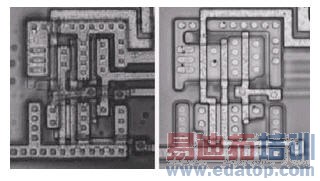

图2是一个NAND闸驱动一个反向器的光学版图照片,类似于该图的不同层照片对于有经验的人无异于电路图。

对于RFID设计来说,射频类比前端需要采用全定制方式实现,但是常采用HDL语言描述来实现包括认证演算法在内的复杂控制逻辑,显然这种采用标准单元库综合的实现方法会加速设计过程,但是也给逆向工程为基础的破坏性攻击提供了极大的便利,这种以标准单元库为基础的设计可以使用电脑自动实现版图重构。因此,采用全定制的方法实现RFID的晶片版图会在一定程度上加大版图重构的难度。

版图重构的技术也适用于获得唯读型ROM的内容。 ROM的位模式储存在扩散层,用氢氟酸(HF)去除晶片各覆盖层后,根据扩散层的边缘就很容易辨认出ROM的内容(图3)。

基于微处理器的RFID设计中,ROM中可能不包含任何加密的密钥资讯,但是它的确包含足够的I/O、存取控制、加密程式等资讯,这些在非破坏性攻击中尤为重要。因此,对于使用微处理器的RFID设计,推荐优先使用FLASH或EEPROM等非挥发性记忆体存放程式。

b.记忆体读出技术

对于存放密钥、用户数据等重要内容的非挥发性记忆体,它们不能透过简单的光学照片获得其中的资讯。在安全认证过程中,至少存取这些数据区一次,因此,可以使用微探针监听汇流排上的讯号获取重要数据。对于良好的设计,简单重覆认证还不足以存取记忆体所有的关键位置。例如,在同一个卡中使用不同的加密密钥和加密演算法,然后在它们之间每隔几周就切换一次,晶片的演算法和密钥的存放区域在没有被广播呼叫启动以前不能被处理器控制等等,因而使早期的被动监测汇流排难以发现这些秘密。这些接触智慧卡IC的经验可以应用于RFID设计中。

一些文献提到,为了保证记忆体数据的完整性,需要在每次晶片复位之后运算并检验一下记忆体的校验结果,其实这种做法给攻击提供了快速存取全部记忆体的方法。

在使用带微处理器的RFID中,还需要考虑软体设计人员为提高程式码效率滥用CPU元件(如地址计数器)的行为所导致的安全问题。程式计数器在每个指令周期都自动增量,如果被用于记忆体读写的地址产生器,攻击中只需防止处理器执行JUMP、CALL和RETURN等指令扰乱正常的读顺序即可。即稍微用雷射切断一些电路连接,改动指令译码器、程式计数器电路即可实现完全存取记忆体的目的。

2.非破坏性攻击及其防范

非破坏性攻击主要针对具有微处理器的产品而言。微处理器本质上是成百上千个触发器、暂存器、锁存器和SRAM单元的集合,这些元件定义了处理器的目前状态,结合组合逻辑则可知道下一时脉的状态。许多类似系统的类比效应适用于非侵入式的攻击,其中:

a.每个电晶体和连线都具有电阻和电容器特性,其温度、电压等特性决定了讯号的传输延迟。由于生产制程参数的分散性,这些数值在单个晶片,或同种产品的不同晶片上差异很大。

b.触发器在很短的时间间隔内采样并和阈值电压比较(与电源相关)。采样的时间间隔相对于时脉边沿是固定的,但不同的触发器之间可能差异很大。

c.触发器仅在组合逻辑稳定后的前一状态上设立新的稳态。

d.在CMOS闸的每次翻转变化过程中,P和N管都会开启一个短暂的时间,因而在电源上造成一次短路。没有翻转的时刻,则电源电流很小。

e.当输出改变时,电源电流会根据负载电容器充放电变化。

1.电流分析攻击

根据电流分析攻击实施的特点,可分为简单电源攻击(SPA)和差分电源攻击。

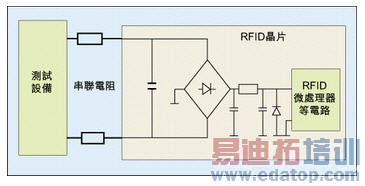

原则上,RFID的电源是整合在AFE的内部,似乎远离了电流分析的危险,然而实际上并非如此。图4显示了RFID接触法测试的原理图:透过在RFID天线和串联的分压电阻两端直接加载符合规格的交流讯号,RFID负载反馈讯号可以百倍于无线模式下的讯号强度直接叠加在加载的交流讯号上。由于晶片的功耗变化与负载调变在本质上是相同的,因此,如果AFE的电源设计不恰当,RFID微处理执行不同内部处理的状态可能在串联电阻的两端交流讯号上反映出来。

对于RFID而言,功耗是晶片设计过程中关心的重要问题,串联方案的效率更高,更适合积体电路设计。但是就安全而言,并联方案是更理想的选择:透过并联释放电路将电源幅度和纹波的变化控制在尽可能小的范围内,使电源电流消耗波动抑制在整流电路之后。这样天线两端的交流讯号不能反应任何内部基频系统(主要是微处理器)状态的差异。

2.故障攻击

透过故障攻击可以导致一个或多个触发器位于病态,因而破坏传输到暂存器和记忆体中的数据。在所知的CPU智慧卡非破坏性攻击中,故障攻击是实际应用中最有效的技术之一。目前有三种技术可以可靠地导致触发器病态且影响很少的机器周期:瞬态时脉、瞬态电源以及瞬态外部电场。

大多数RFID的时脉、电源都是使用天线的交流讯号整形得到的,因此透过改变交流讯号谐波的幅度、对称性、频率等参数可以实施时脉-电源故障攻击。借助于RFID接触测试设备中的数位直接合成交流讯号技术,很容易产生时脉-电源故障攻击所需的波形。

RFID产品为了有效抵御时脉故障攻击,除了采用时脉探测器以外,更重要的是严格限制RFID设计工作频率范围、载频的谐波品质因素、对称性等指标。因此,从安全角度来说,并非RFID对机具适应能力越强越好。

潜在的故障技术仍需进一步探索,如透过将金属探针置于处理器几百个微米高度的时候,在几个毫秒内施加几百伏的电压,得到的电场强度足够改变附近的电晶体阈值电压。这些技术的应用价值和应对措施还有待进一步的研究。

RFID的测试态及保护

对于一般意义的积体电路产业链来说,需要将不良的晶片在晶圆测试阶段剔除以减少后端加工程序中不必要的浪费,RFID晶片也不例外。根据RFID晶片的特点,晶圆测试内容包括:RF性能测试、逻辑功能测试和记忆体测试。和普通晶片一样,如果借助于晶片应用功能来进行片上逻辑和记忆体测试,则测试成本将大幅增加。通常采取等效测试原理设计额外的测试态来快速完成。由于测试态提供了快速、全面存取记忆体的机制,因此有必要在晶圆测试完成后,将测试态永久关闭。

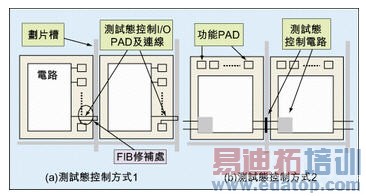

图5a是在接触式智慧卡晶片的发展过程中曾大量采用的测试态控制方式:使用额外的I/O接脚和晶片内部电路相连,该连线经过划片槽,这样晶片划断后就不能透过简单控制该接脚进入测试态。由于FIB修补技术的出现,这个方法已经过时。图5b是最有潜力的替代方案:在划片槽和邻近的晶片中设计部份控制电路,因而得到不可逆的测试态控制方法。

本文总结

本文对RFID晶片设计安全从破坏性、非破坏性攻击以及测试态控制三个方面作了简单探讨,透过与接触式智慧卡晶片安全设计比较,提供一些应对的设计措施。然而仍然有很多安全设计措施不能一一列举,如用于对付功率分析的电流调节器和噪音负载。中国大陆第二代居民身份证即将实施,这将是世界上最大的RFID计画,考虑其晶片设计安全问题具有重要的现实意义。

作者:卢小冬

计划主管

Email: luxd@dmt.com.cn

大唐微电子公司智慧卡IC设计部

周东平

高级工程师

Email: zhou_dp@fri.com.cn

公安部第一研究所

以前,人们普遍认为由于采用了各种复杂的认证演算法、密钥等来保护数据免受未获授权使用,IC卡具有磁卡无法比拟的安全性能。但在90年代中期,大部份的IC卡处理器都被成功地实施了逆向工程,因此这个看法有了很大的改变。除了采用更新的设计技术以外,更重要的是在IC卡晶片设计与实现过程中考虑抗攻击措施,以保护重要的数据不被非法使用。

从结构上讲,RFID是一个包含射频类比前端(RF AFE)和基频讯号处理两大部份的单片积体电路(见图1)。基频系统包括控制逻辑(甚至微处理器)和必要的记忆体,AFE部份是RFID的能量与讯号介面,提供片上基频系统工作所需的电源和时脉等辅助讯号,完成数据的接收与发送功能。由于RF AFE屏蔽了智慧卡片上的电源、时脉、上电复位(POR)等讯号与外界的联系,在一定程度上减少了攻击实施的点,与接触式智慧卡相较在安全性方面有一定的提升。

智慧卡晶片攻击技术及应对措施

根据是否破坏智慧卡晶片的实体封装可以将智慧卡的攻击技术分为两大类:破坏性攻击和非破坏性攻击。

破坏性攻击和晶片逆向工程在最初的步骤上是一致的:使用发烟硝酸去除包裹晶片的环氧树脂;用丙酮/去离子水/异丙醇完成清洗;氢氟酸超声浴进一步去除晶片的各层金属。在去除晶片封装之后,透过金丝键合恢复晶片功能焊盘与外界的电气连接,最后可以使用手动微探针获取感兴趣的讯号。对于深次微米以下的CMOS产品,通常具有3层以上的金属连线,为了解晶片的内部结构,可能要逐层去除以获得重构晶片版图设计所需的资讯。在了解内部讯号走线的基础上,聚焦离子束(FIB)修补技术甚至适用于将感兴趣的讯号连到晶片的表面供进一步观察。

非破坏性攻击主要针对具有微处理器的产品,其方法主要包括软体攻击、窃听技术和故障产生技术。软体攻击使用微处理器的通用通讯介面,寻求安全协议、加密演算法以及他们实体实现的弱点;窃听技术采用高时域精密度的方法,分析电源介面在微处理器正常工作过程中产生的各种电磁辐射的类比特征;故障产生技术藉由产生异常的应用环境条件,使处理器产生故障,因而获得额外的存取途径。

智慧卡的攻击一般从破坏性的反向工程开始,其结论可以用于开发廉价和快速的非破坏性攻击方法,这是最常见的最有效的智慧卡攻击模式之一。

1.破坏性攻击及其防范

a.版图重构

破坏性攻击的一个重要步骤是重构目标晶片的版图。透过研究连接模式和追踪金属连线穿越可见模组(如ROM、RAM、EEPROM、ALU、指令译码器等)的边界,可以迅速识别晶片上的一些基本结构,如数据线和地址线。

图2是一个NAND闸驱动一个反向器的光学版图照片,类似于该图的不同层照片对于有经验的人无异于电路图。

对于RFID设计来说,射频类比前端需要采用全定制方式实现,但是常采用HDL语言描述来实现包括认证演算法在内的复杂控制逻辑,显然这种采用标准单元库综合的实现方法会加速设计过程,但是也给逆向工程为基础的破坏性攻击提供了极大的便利,这种以标准单元库为基础的设计可以使用电脑自动实现版图重构。因此,采用全定制的方法实现RFID的晶片版图会在一定程度上加大版图重构的难度。

版图重构的技术也适用于获得唯读型ROM的内容。 ROM的位模式储存在扩散层,用氢氟酸(HF)去除晶片各覆盖层后,根据扩散层的边缘就很容易辨认出ROM的内容(图3)。

基于微处理器的RFID设计中,ROM中可能不包含任何加密的密钥资讯,但是它的确包含足够的I/O、存取控制、加密程式等资讯,这些在非破坏性攻击中尤为重要。因此,对于使用微处理器的RFID设计,推荐优先使用FLASH或EEPROM等非挥发性记忆体存放程式。

b.记忆体读出技术

对于存放密钥、用户数据等重要内容的非挥发性记忆体,它们不能透过简单的光学照片获得其中的资讯。在安全认证过程中,至少存取这些数据区一次,因此,可以使用微探针监听汇流排上的讯号获取重要数据。对于良好的设计,简单重覆认证还不足以存取记忆体所有的关键位置。例如,在同一个卡中使用不同的加密密钥和加密演算法,然后在它们之间每隔几周就切换一次,晶片的演算法和密钥的存放区域在没有被广播呼叫启动以前不能被处理器控制等等,因而使早期的被动监测汇流排难以发现这些秘密。这些接触智慧卡IC的经验可以应用于RFID设计中。

一些文献提到,为了保证记忆体数据的完整性,需要在每次晶片复位之后运算并检验一下记忆体的校验结果,其实这种做法给攻击提供了快速存取全部记忆体的方法。

在使用带微处理器的RFID中,还需要考虑软体设计人员为提高程式码效率滥用CPU元件(如地址计数器)的行为所导致的安全问题。程式计数器在每个指令周期都自动增量,如果被用于记忆体读写的地址产生器,攻击中只需防止处理器执行JUMP、CALL和RETURN等指令扰乱正常的读顺序即可。即稍微用雷射切断一些电路连接,改动指令译码器、程式计数器电路即可实现完全存取记忆体的目的。

2.非破坏性攻击及其防范

非破坏性攻击主要针对具有微处理器的产品而言。微处理器本质上是成百上千个触发器、暂存器、锁存器和SRAM单元的集合,这些元件定义了处理器的目前状态,结合组合逻辑则可知道下一时脉的状态。许多类似系统的类比效应适用于非侵入式的攻击,其中:

a.每个电晶体和连线都具有电阻和电容器特性,其温度、电压等特性决定了讯号的传输延迟。由于生产制程参数的分散性,这些数值在单个晶片,或同种产品的不同晶片上差异很大。

b.触发器在很短的时间间隔内采样并和阈值电压比较(与电源相关)。采样的时间间隔相对于时脉边沿是固定的,但不同的触发器之间可能差异很大。

c.触发器仅在组合逻辑稳定后的前一状态上设立新的稳态。

d.在CMOS闸的每次翻转变化过程中,P和N管都会开启一个短暂的时间,因而在电源上造成一次短路。没有翻转的时刻,则电源电流很小。

e.当输出改变时,电源电流会根据负载电容器充放电变化。

1.电流分析攻击

根据电流分析攻击实施的特点,可分为简单电源攻击(SPA)和差分电源攻击。

原则上,RFID的电源是整合在AFE的内部,似乎远离了电流分析的危险,然而实际上并非如此。图4显示了RFID接触法测试的原理图:透过在RFID天线和串联的分压电阻两端直接加载符合规格的交流讯号,RFID负载反馈讯号可以百倍于无线模式下的讯号强度直接叠加在加载的交流讯号上。由于晶片的功耗变化与负载调变在本质上是相同的,因此,如果AFE的电源设计不恰当,RFID微处理执行不同内部处理的状态可能在串联电阻的两端交流讯号上反映出来。

对于RFID而言,功耗是晶片设计过程中关心的重要问题,串联方案的效率更高,更适合积体电路设计。但是就安全而言,并联方案是更理想的选择:透过并联释放电路将电源幅度和纹波的变化控制在尽可能小的范围内,使电源电流消耗波动抑制在整流电路之后。这样天线两端的交流讯号不能反应任何内部基频系统(主要是微处理器)状态的差异。

2.故障攻击

透过故障攻击可以导致一个或多个触发器位于病态,因而破坏传输到暂存器和记忆体中的数据。在所知的CPU智慧卡非破坏性攻击中,故障攻击是实际应用中最有效的技术之一。目前有三种技术可以可靠地导致触发器病态且影响很少的机器周期:瞬态时脉、瞬态电源以及瞬态外部电场。

大多数RFID的时脉、电源都是使用天线的交流讯号整形得到的,因此透过改变交流讯号谐波的幅度、对称性、频率等参数可以实施时脉-电源故障攻击。借助于RFID接触测试设备中的数位直接合成交流讯号技术,很容易产生时脉-电源故障攻击所需的波形。

RFID产品为了有效抵御时脉故障攻击,除了采用时脉探测器以外,更重要的是严格限制RFID设计工作频率范围、载频的谐波品质因素、对称性等指标。因此,从安全角度来说,并非RFID对机具适应能力越强越好。

潜在的故障技术仍需进一步探索,如透过将金属探针置于处理器几百个微米高度的时候,在几个毫秒内施加几百伏的电压,得到的电场强度足够改变附近的电晶体阈值电压。这些技术的应用价值和应对措施还有待进一步的研究。

RFID的测试态及保护

对于一般意义的积体电路产业链来说,需要将不良的晶片在晶圆测试阶段剔除以减少后端加工程序中不必要的浪费,RFID晶片也不例外。根据RFID晶片的特点,晶圆测试内容包括:RF性能测试、逻辑功能测试和记忆体测试。和普通晶片一样,如果借助于晶片应用功能来进行片上逻辑和记忆体测试,则测试成本将大幅增加。通常采取等效测试原理设计额外的测试态来快速完成。由于测试态提供了快速、全面存取记忆体的机制,因此有必要在晶圆测试完成后,将测试态永久关闭。

图5a是在接触式智慧卡晶片的发展过程中曾大量采用的测试态控制方式:使用额外的I/O接脚和晶片内部电路相连,该连线经过划片槽,这样晶片划断后就不能透过简单控制该接脚进入测试态。由于FIB修补技术的出现,这个方法已经过时。图5b是最有潜力的替代方案:在划片槽和邻近的晶片中设计部份控制电路,因而得到不可逆的测试态控制方法。

本文总结

本文对RFID晶片设计安全从破坏性、非破坏性攻击以及测试态控制三个方面作了简单探讨,透过与接触式智慧卡晶片安全设计比较,提供一些应对的设计措施。然而仍然有很多安全设计措施不能一一列举,如用于对付功率分析的电流调节器和噪音负载。中国大陆第二代居民身份证即将实施,这将是世界上最大的RFID计画,考虑其晶片设计安全问题具有重要的现实意义。

作者:卢小冬

计划主管

Email: luxd@dmt.com.cn

大唐微电子公司智慧卡IC设计部

周东平

高级工程师

Email: zhou_dp@fri.com.cn

公安部第一研究所