- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的UHF的RFID读写器设计

录入:edatop.com 点击:

1 引 言

射频识别技术(RFID)是利用射频方式进行远距离通信以达到物品识别目的,可用来追踪和管理几乎所有物理对象。在工业自动化、商业自动化、交通运输控制管理、防伪等众多领域,甚至军事用途都具有广泛的应用前景,并且引起了广泛的关注。RFID系统一般包括读写器和电子标签(或称应答器)2个部分。RFID电子标签(Tag)由芯片与天线(Antenna)组成,每个标签具有惟一的电子编码。标签附在物体上以标识目标对象。RFID读写器(Reader)的主要任务是控制射频模块向标签发射读写信号,并接收标签的应答。对标签信息进行解码,并将信息传输到主机以供处理。根据应用的不同,阅读器可以是手持式或固定式。本文重点介绍的就是读写器的开发。

EPC规范已经颁布第一代规范。规范把标签细分为Class 0,Class 1,Class 2三种。其中Class 0和Class 1标签都是一次写入多次读取标签,Class 0标签只能由厂商写入信息,用户无法修改,因而又称为只读标签,主要用于供应链管理)Class 1则提供了更多的灵活性,信息可由用户写入一次。Class 0和Class 1标签采用不同的空中接口标准进行通信,因此两类标签不能互操作。Class 2标签具备多次写入能力,并增加了部分存储空间用于存储用户的附加数据。Class 2标签允许加入安全与访问控制、感知网络和Ad Hoc网络等功能支持。目前EPCglobal正在制定第二代标签标准,即UHF Class l Generation 2(C1G2)。C1G2具有随时更新标签内容的能力,保证标签始终保存最新信息。EPC规范l_0版本包括EPC Tag数据规范、Class 0(900 MHz)标签规范、C1ass 1(13.56 MHz)标签接口规范、Class l(860~930 MHz)标签射频与逻辑通讯接口规范、物理标识语言(PhysicalMarkup Language,PML)。

本文重点介绍EPC Class 1读写器系统设计、数字部分设计及FPGA在数字实现上的应用。由于U 频段RFID技术的应用还处在早期的发展阶段,符合EPCClass 1协议的读写器在国内还没有相关产品面世。本文对相关开发有一定的参考价值。

2 EPC Class lb系统设计

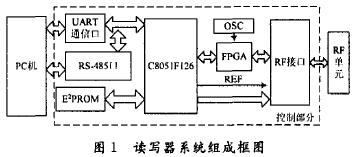

一个完整的RFID系统包括:读写器、天线、标签和PC机。读写器完成对标签(Tag)的读写操作。通过RS 232或RS 485总线完成PC机的命令接收和EPC卡号的上传。图l是读写器的系统组成框图。读写器组成包括与PC机的串口通信部分、单片机和FPGA组成的数字部分、射频部分。RF单元实现和标签的通信,数字部分完成对射频部分的控制、回波命令解析 PC机接收卡号实现上位机的控制。下面对各模块做简单介绍。

2.1 PC 端

RFID系统一般要将标签信息读取到计算机上,然后等待处理 用户通过PC机可以实现读写器控制,完成对标签的读写操作。读写器与PC机通信是基于RS 232总线,纠错算法是CRC—CCITT算法。

-图1-

2.2 射频模块

读写器对标签的读写是通过发送射频能量和对回波实现的。射频模一方面将数字模块送来的信息完成调制并发送。标签应答,射频模块接收回波信号将他解调成基带信号,送到数字模块。

2.3 数字模块

数字模块由单片机(cygnal C8O51F126)、存储器(24Cz56),FPGA(xl SlOO)组成 单片机的功能有:

(1)实现与PC机通信,接收PC机命令,完成解析下传到FPGA

(2)将FPGA送来的EPC卡号加算CRC—CCITT校验上传PC机。择Xilinx公司ISE6.2,仿真软件为Modelsim 5.7。设计实现采取原理图和VHDL语言相结合的原则。顶层模块采用原理图设计,功能模块采用VHDL语言实现。

(3)解决多卡碰撞,实现多卡读取。由于FPGA实现多卡读取算法非常消耗FPGA资源,而且需要FPGA有大量的存储器资源存放读到的卡号,成本较高。而如果由PC机实现多卡读取算法,则读取速度很难提高。

(4)实现对射频模块的锁相环频率控制以及功率控制 读写器发射功率常需要调整,而且读写器有时需要在不同射频频率,甚至跳频下工作。单片机通过对射频模块的锁相环控制实现对射频频率和功率的控制。

单片机采用CYGNAL公司的C8051F126。内部有128 k的FLASH存储器和8 k的RAM,可以在5O MHz主频下工作。

FPGA实现EPC Class l通信协议,接收单片机控制命令,将命令按照协议标准编码送到射频模块调制并发送,然后解调并接收射频模块送来的回波基带信号,将得到的标签信息发送给单片机。FPGA实现的EPC Class l命令的基本命令包括scrollid,scrollallid,pinged,quiet,talk,kill;编程命令programid,verifyid,lockid,eraseid 这些命令包括命令的发送和回波的解析。根据发送命令不同,对应的发送命令格式也不相同,分为2类。回波信号格式也根据命令的不同分为2类。下面介绍FPGA实现的EPC Class 1协议。

3 FPGA实现的信号调制解调

3.1 FPGA 器件及开发平台

FPGA选择Xilinx公司的SPART II XC2S100规模为1O万门,系统时钟选择40 MHz,满足要求。开发软件选择Xilinx公司ISE6.2,仿真软件为Modelsim 5.7。设计实现采取原理图和VHDL语言相结合的原则。顶层模块采用原理图设计,功能模块采用VHDL语言实现

3.2 结构框图

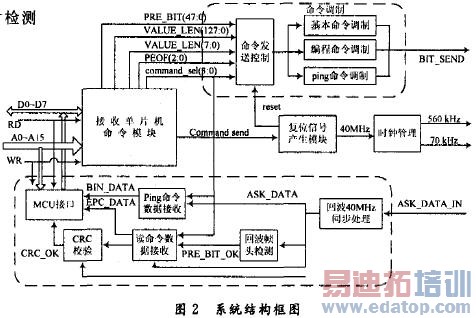

从系统的结构图可以看出FPGA实现的调制解调部分包括:单片机接口(单片机的命令接收模块、向单片机发送数据模块)、复位信号产生模块、命令调制模块、命令接收模块。

-图2-

单片机向FPGA发送数据采用对地址操作方式,单片机对FPGA读取数据采用查询方式。FPGA整个工作过程:FPGA接收单片机控制命令,接收单片机命令模块将所收到的命令赋值给相应寄存器,同时复位信号产生模块根据单片机发送的命令产生复位信号(单片机写FPGA过程即为复位)。命令调制模块根据单片机送来的命令以及相应控制字,输出相应的调制信号(bit— sent)输出到射频模块。接收模块始终在检测回波数据,当检测到回波数据的帧头有效时通知读命令数据接收模块接收数据。同时将接收到的数据送CRC校验模块校验,数据接收完成,CRC校验也即完成,CRC校验模块校验成功即产生CRCOK= l 表示读卡号成功,单片机查询到此位为高时通过MCU接口模块读卡号和CRC。在Ping命令时,Ping命令接收模块判断命令发送模块此时发送的命令类型。如果为Ping命令时,则接收数据,将接收的各槽数据及状态信息放在BIN DATA寄存器中。

3.3 关键功能模块

(1)命令调制模块

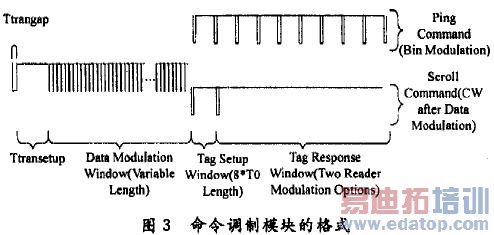

命令调制模块发送的命令必须符合EPC规范对信息编码要求以及命令格式要求。信息编码占空比为1/8时钟表示“0”,占空比为3/8时钟表示“l”。命令格式要求如图3所示,根据EPC规范,可以将命令格式分为3种,分别为ping命令格式、写卡(program)命令格式、读卡(scrolled)命令格式,具体命令格式参照文献[1]。命令调制模块实现3种命令格式的调制。命令调制模块设计采

-图3-

(2)Ping命令接收模块

回波编码和发送编码方式不同,Ping命令和scrollid命令回波编码用“1010”表示 l ,用“l100”表示 0。接收数据模块必须将回波调制信号解调成~0, 1 信号。Ping命令是基本多卡操作命令。如图3所示,Ping命令的标签应答是在8个槽(bin)中应答,对应着不同的8组标签。这样一次Ping命令可以判断8组标签。提高了多卡效率.每一个槽(bin)信息用2个寄存器表示,BIN0(1:O)表示卡的状态信息:有卡、无卡、多卡。BIN(7:O)表示槽的数据。单片机根据槽状态信息决定是否读取槽数据.

(3)scollid命令数据接收模块

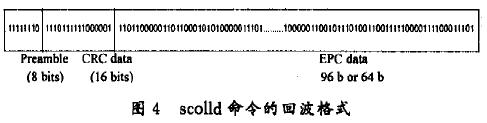

scrollid以及scrollallid,verifyid命令的回波格式相同,接收方式相同.回波格式如图4所示

-图4-

一帧完整回波包括帧头(F7H),16位CRC,96位或64位EPC DATA。接收模块采用检测帧头的方式,通过一个32位移位寄存器(1 b数据由4个状态信息表示)检测帧头,帧头有效则读数据模块解调回波数据,解调数据存储在EPC DATA寄存器中。同时将检测到的bits送到CRC校验。

(4)CRC校验模块

CRC模块对数据接收模块检测到的数据按照CRC—CCITT算法校验,校验通过则产生CRC OK=”1”。单片机根据此状态读取EPC DATA。CRC—CCITT算法实现采用串行方式。程序非常简单,而且节省FPGA资源。

节选代码如下:

xOr_flag_en: process(elk)begin

if elk== ‘0’ and elk event then

if en ==’l’ then

if crc_bur(15)== ‘1’ then

crc bur< = (crc bur(14 downto O)&data_in)

xor”OOO1OOOOOO1OOOO1”:

xor_flag<= ‘l’

else erc_buf <=crc_buf(14 downto O)&data_in :

xor_flag< = ‘0’;

end if;

else crc_buf< =”111ll111111llll1”;

endif;

endif;

end prOcess

4 结语

FPGA实现了对EPC Classl 96位和64位卡的读写操作命令,读写成功率非常高,能实现8 m距离的正常读,多卡读取速度快。读写器和标签的读写速率为上行70 kb/s,下行140 kb/s。此读写器也已经在批量生产,投放市场。

在读写器设计过程中仍有几方面问题需要进一步改善。一是Ping命令回波没有CRC校验,所以Ping命令的回波检测成功率不够高,影响多卡速度;另一方面,当回波信号信噪比不高时,接收成功率下降速度很快。同时,在读写器设计过程中发现EPC标签的一些问题。其中突出的是,调试发现96位标签在应答时存在累积周期差,不能和读写器的时钟同步。标签锁相环不够准确,给读写器的设计带来不小难度.