- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

前进中的晶圆级3D集成

录入:edatop.com 点击:

3D集成是指将多层平面器件堆叠起来,并通过穿透硅的Z方向通孔实现互连的系统级集成方案。

从概念上来讲,3D集成能够在减少芯片面积的同时缓解互连延迟问题。如果用垂直方向的短互连线来代替二维结构中大量的长互连线,就能够使逻辑电路的性能大大提高。例如,通过将关键路径上的逻辑门放置在多个有源层上,就能够将它们非常紧密地排布起来。也可以将电压和/或性能要求不同的电路放置在不同的层上。

3D晶圆堆叠基于具有特定功能的全晶圆产品(即嵌入式处理器、DSP、SRAM、DRAM、嵌入式无线网络等),并将这些晶圆或分立的已知良好芯片(known good die,KGD)垂直地互连起来,制作成一个功能器件。3D结构能够集成许多别的方法无法兼容的技术,这样就可以显著地提升器件的性能、功能性和波形因数。这种3D堆叠能够令人信服地集成天线、传感器、电源管理和电源存储器件等技术。3D集成缩短了芯片间的信号路径,允许系统更快地运行,从而提高系统性能和降低功耗。互连线长度是电源应用中要考虑 的重要因素,保持足够短的互连线长度非常有利于降低功耗。当采用这种3D堆叠芯片方案时,最需要关心的是散热问题,不过由于通孔的使用缩短了总的互连线长度,这实际上在一定程度上减小了热的产生。

在最近的电子元器件技术会议(ECTC)上有许多介绍3D晶圆级集成进展的报告。在会议的小组讨论中,用于晶圆到晶圆(W2W)和芯片到晶圆(D2W)互连的最新3D前沿进展被总结出来。很多与会者都注意到,早先的W2W键合概念正被D2W键合所逐步取代,因为D2W具有以下优势:

■ 只封装KGD

■ 排列对准的容忍度更大

■ 具有将尺寸差别很大的芯片互连起来的能力

■ 具有为“异类集成”而将尺寸差别很大的芯片互连起来的能力

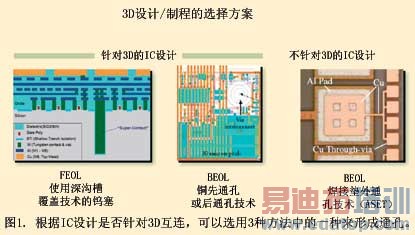

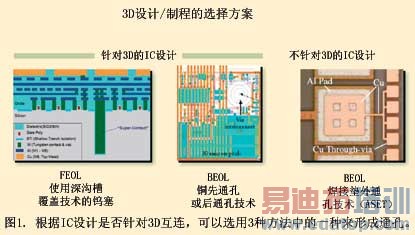

根据IC设计是否针对3D互连,目前已有3种可行的选择方案来形成通孔(图1)。

针对3D的IC设计:使用FEOL通孔

如果芯片是针对3D应用设计的,那么就可以使用任何目前实际用于(嵌入式)DRAM深沟槽电容技术的设备来制作前段制程(FEOL)通孔。目前用于3D互连的通孔直径一般为2-4mm,而且还可以更小一些。这是初创公司Tezzaron为他们的“超接触”技术所选择的路线。既然通孔与IC互连是同时制作在晶圆上的,那么就没有必要额外留出一些不进行片上互连布线的区域。在完成FEOL通孔的制作之后将晶圆减薄,直到通孔(一般是钨,也可能是铜)从晶圆背面暴露出来,然后布线并制作背面焊接垫来将晶圆互连到其它的芯片/晶圆上。

针对3D的IC设计:使用BEOL通孔

如果选择后段制程(BEOL)来制作通孔,那么在IC的设计和制造过程中必须留出额外的区域。这样,3D 晶圆代工厂/封装厂就可以通过刻蚀这些保留区域而得到通孔。共有两种方法:先刻蚀得到通孔,再装配到操作晶圆上,然后减薄(先通孔方法,via-first);或先将晶圆键合到另一个芯片/晶圆,然后再刻蚀得到通孔(后通孔方法,via-last)。初创公司ZyCube是BEOL先通孔技术的倡导者,IBM则支持BEOL后通孔技术。

不针对3D的IC设计:使用BEOL通孔

如果芯片/晶圆已经存在而无法重新设计,那么就需要在外围焊接垫和划线迹道之间的区域重新分布通孔;这种技术是超高级电子技术联盟(ASET)开发的。任何具备Bosch刻蚀能力的封装或MEMS代工厂都能完成这种制程。人们也许会考虑将绝缘的通孔直接连通到外围焊接垫。然而,最近出现了一种在焊接垫下放置支撑柱的方法,可以更好地防止易碎的低k层间介质(ILD)在引线键合过程中破裂,从而排除了前面那种通孔直连焊接垫的选择。

在同一个会议上,来自Research Triangle Institute(RTI)的Christopher Bower介绍了DARPA VISA(垂直互连传感器阵列)项目的最新进展。VISA是一种使用BEOL后通孔方法的D2W 3D集成技术,正由RTI和DRS Infrared Technologies公司合作开发。

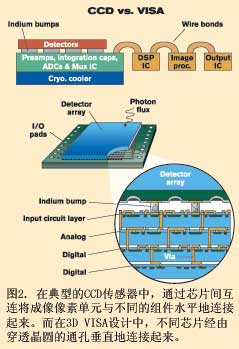

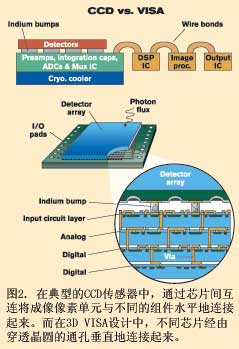

在典型的电荷耦合器件(CCD)传感器中,通过芯片间的互连将成像像素单元与A/D转换器、DSP、图像处理器和输出IC等组件水平地连接起来(图2)。不过这种互连方法限制了取样速率和分辨率。而在3D VISA设计中,这些芯片经由穿透晶圆的通孔垂直地连接起来(图2)。

VISA制造流程从预留出通孔区域的IC晶圆开始,这些晶圆是在标准的CMOS工厂中制造的。接着在第一片晶圆(IC1晶圆)上淀积金属再分布层并形成图形,然后将第二片晶圆(IC2晶圆)面朝下地安放到操作晶圆上,并用背部打磨和化学机械抛光(CMP)等方法来将其减薄。当减薄后的IC2晶圆仍然在操作晶圆上时就被切割开来得到芯片,而独立的KGD则被键合到IC1晶圆上的已知良好的点。

然后依次进行以下步骤:光刻定义出垂直互连的刻蚀掩模,并刻蚀得到穿透IC2层的、高深宽比的4mm通孔;淀积一层保角的绝缘体,并选择性地移除通孔底部的绝缘体以清洁金属焊接垫;淀积金属来填充垂直互连。最后,顶层金属被图形化和钝化,为连接后续的IC层做好准备。

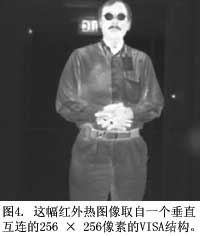

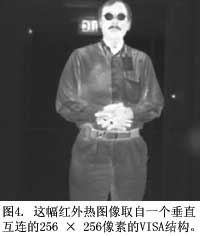

如图3所示是由上述方法制造的堆叠的截面SEM照片,这个堆叠由两层IC构成。这幅照片的拍摄是在垂直互连完成之后,而在顶层金属的图形化和钝化之前。顶部IC层(IC2)的厚度约30mm,包含约10mm的SiO2 IC ILD和20mm的硅,其背面有一个薄的钝化层。通过使用高精度的、带有分光棱镜的芯片键合机和聚合物粘接剂,将IC2层键合到下面的IC1层上。两个IC层之间的后键合(post-bond)对准精度通常>2mm。通过高深宽比(约8:1)的、直径为4mm的铜垂直互连线,将分立的IC层互连起来。而通过保角的介质层将这些垂直互连与衬底硅绝缘。如图4所示的红外热图像取自一个垂直互连的256 × 256像素的VISA结构。

从概念上来讲,3D集成能够在减少芯片面积的同时缓解互连延迟问题。如果用垂直方向的短互连线来代替二维结构中大量的长互连线,就能够使逻辑电路的性能大大提高。例如,通过将关键路径上的逻辑门放置在多个有源层上,就能够将它们非常紧密地排布起来。也可以将电压和/或性能要求不同的电路放置在不同的层上。

3D晶圆堆叠基于具有特定功能的全晶圆产品(即嵌入式处理器、DSP、SRAM、DRAM、嵌入式无线网络等),并将这些晶圆或分立的已知良好芯片(known good die,KGD)垂直地互连起来,制作成一个功能器件。3D结构能够集成许多别的方法无法兼容的技术,这样就可以显著地提升器件的性能、功能性和波形因数。这种3D堆叠能够令人信服地集成天线、传感器、电源管理和电源存储器件等技术。3D集成缩短了芯片间的信号路径,允许系统更快地运行,从而提高系统性能和降低功耗。互连线长度是电源应用中要考虑 的重要因素,保持足够短的互连线长度非常有利于降低功耗。当采用这种3D堆叠芯片方案时,最需要关心的是散热问题,不过由于通孔的使用缩短了总的互连线长度,这实际上在一定程度上减小了热的产生。

在最近的电子元器件技术会议(ECTC)上有许多介绍3D晶圆级集成进展的报告。在会议的小组讨论中,用于晶圆到晶圆(W2W)和芯片到晶圆(D2W)互连的最新3D前沿进展被总结出来。很多与会者都注意到,早先的W2W键合概念正被D2W键合所逐步取代,因为D2W具有以下优势:

■ 只封装KGD

■ 排列对准的容忍度更大

■ 具有将尺寸差别很大的芯片互连起来的能力

■ 具有为“异类集成”而将尺寸差别很大的芯片互连起来的能力

根据IC设计是否针对3D互连,目前已有3种可行的选择方案来形成通孔(图1)。

针对3D的IC设计:使用FEOL通孔

如果芯片是针对3D应用设计的,那么就可以使用任何目前实际用于(嵌入式)DRAM深沟槽电容技术的设备来制作前段制程(FEOL)通孔。目前用于3D互连的通孔直径一般为2-4mm,而且还可以更小一些。这是初创公司Tezzaron为他们的“超接触”技术所选择的路线。既然通孔与IC互连是同时制作在晶圆上的,那么就没有必要额外留出一些不进行片上互连布线的区域。在完成FEOL通孔的制作之后将晶圆减薄,直到通孔(一般是钨,也可能是铜)从晶圆背面暴露出来,然后布线并制作背面焊接垫来将晶圆互连到其它的芯片/晶圆上。

针对3D的IC设计:使用BEOL通孔

如果选择后段制程(BEOL)来制作通孔,那么在IC的设计和制造过程中必须留出额外的区域。这样,3D 晶圆代工厂/封装厂就可以通过刻蚀这些保留区域而得到通孔。共有两种方法:先刻蚀得到通孔,再装配到操作晶圆上,然后减薄(先通孔方法,via-first);或先将晶圆键合到另一个芯片/晶圆,然后再刻蚀得到通孔(后通孔方法,via-last)。初创公司ZyCube是BEOL先通孔技术的倡导者,IBM则支持BEOL后通孔技术。

不针对3D的IC设计:使用BEOL通孔

如果芯片/晶圆已经存在而无法重新设计,那么就需要在外围焊接垫和划线迹道之间的区域重新分布通孔;这种技术是超高级电子技术联盟(ASET)开发的。任何具备Bosch刻蚀能力的封装或MEMS代工厂都能完成这种制程。人们也许会考虑将绝缘的通孔直接连通到外围焊接垫。然而,最近出现了一种在焊接垫下放置支撑柱的方法,可以更好地防止易碎的低k层间介质(ILD)在引线键合过程中破裂,从而排除了前面那种通孔直连焊接垫的选择。

在同一个会议上,来自Research Triangle Institute(RTI)的Christopher Bower介绍了DARPA VISA(垂直互连传感器阵列)项目的最新进展。VISA是一种使用BEOL后通孔方法的D2W 3D集成技术,正由RTI和DRS Infrared Technologies公司合作开发。

在典型的电荷耦合器件(CCD)传感器中,通过芯片间的互连将成像像素单元与A/D转换器、DSP、图像处理器和输出IC等组件水平地连接起来(图2)。不过这种互连方法限制了取样速率和分辨率。而在3D VISA设计中,这些芯片经由穿透晶圆的通孔垂直地连接起来(图2)。

VISA制造流程从预留出通孔区域的IC晶圆开始,这些晶圆是在标准的CMOS工厂中制造的。接着在第一片晶圆(IC1晶圆)上淀积金属再分布层并形成图形,然后将第二片晶圆(IC2晶圆)面朝下地安放到操作晶圆上,并用背部打磨和化学机械抛光(CMP)等方法来将其减薄。当减薄后的IC2晶圆仍然在操作晶圆上时就被切割开来得到芯片,而独立的KGD则被键合到IC1晶圆上的已知良好的点。

然后依次进行以下步骤:光刻定义出垂直互连的刻蚀掩模,并刻蚀得到穿透IC2层的、高深宽比的4mm通孔;淀积一层保角的绝缘体,并选择性地移除通孔底部的绝缘体以清洁金属焊接垫;淀积金属来填充垂直互连。最后,顶层金属被图形化和钝化,为连接后续的IC层做好准备。

如图3所示是由上述方法制造的堆叠的截面SEM照片,这个堆叠由两层IC构成。这幅照片的拍摄是在垂直互连完成之后,而在顶层金属的图形化和钝化之前。顶部IC层(IC2)的厚度约30mm,包含约10mm的SiO2 IC ILD和20mm的硅,其背面有一个薄的钝化层。通过使用高精度的、带有分光棱镜的芯片键合机和聚合物粘接剂,将IC2层键合到下面的IC1层上。两个IC层之间的后键合(post-bond)对准精度通常>2mm。通过高深宽比(约8:1)的、直径为4mm的铜垂直互连线,将分立的IC层互连起来。而通过保角的介质层将这些垂直互连与衬底硅绝缘。如图4所示的红外热图像取自一个垂直互连的256 × 256像素的VISA结构。

本文作者:Philip Garrou ,IEEE院士、IEEE CPMT协会主席,RTI International项目顾问。

13.56MHz NFC天线,13.56MHz RFID天线设计培训课程套装,让天线设计不再难

上一篇:初探无线城市指标

下一篇:RFID多义性路径识别系统