- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ARM智能交通信号机控制板开发

录入:edatop.com 点击:

1 引言

目前我国的城市交通控制主要还是靠道路交通信号控制机(以下简称信号机)。国内的信号机主要分为两类:一类采用8/16位单片机作为处理器,交通控制功能简单、方案单一,以RS 232或RS485为通讯方式,难以与控制中心联网以及实现区域交通协调控制等功能,不能适应现代化大路口交通控制的要求;另一类则是基于工控机或PC104,功能虽然强大,但由于工控机或PC104都是按通用计算机标准设计,并非专门针对信号机应用设计,该类信号机硬件结构复杂且很多功能并不需要,成本也高,国外的信号机(如西门子公司的2070和美国的EAGLE)开发起步早,水平高,已有各种自适应联网型信号机产品,但一般不适用于中国混合交通的实际情况,且价格昂贵,操作不方便。

信号机是一个典刑的嵌入式系统,嵌入式系统是以应用为中心来设计,对功能、性能、可靠性、成本、功耗、体积等有严格的要求,既要满足智能交通系统对信号机智能化、多功能的要求,又要最大化信号机的性价比,因此本设计选择基于ARM核的32位嵌入式RISC处理器——AT91RM9200来完成智能交通信号机控制板的硬件设计,以达到使信号机在交通系统中成为收集与处理交通流量数据、通信联网以及区域协调控制平台的设计目标。

2 信号机系统硬件设计

2.1 系统总体硬件结构

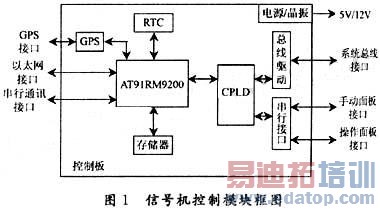

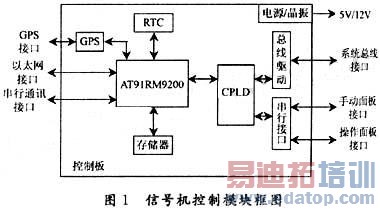

智能交通系统要求信号机可以向控制中心实时提供多种道路信息和车流量数据信息,接收控制中心的控制命令,并能够独立执行一些复杂的算法,可以根据交通流量变化实时条件路口信号灯的绿灯时间,因此考虑现有信号机的不足,根据信号机功能发展的趋势和要求,本文设计的信号机控制板具有控制参数输入、控制状态输出、控制参数保存、灯态输出控制、交通流信息(主要是车流量)实时检测与历史数据存储、多种灯态控制方案与算法模型存储、支持以太网及与手持终端设备通讯等基本功能。整个系统硬件结构如图1所示。

2.1.1 AT91RM9200微处理器介绍

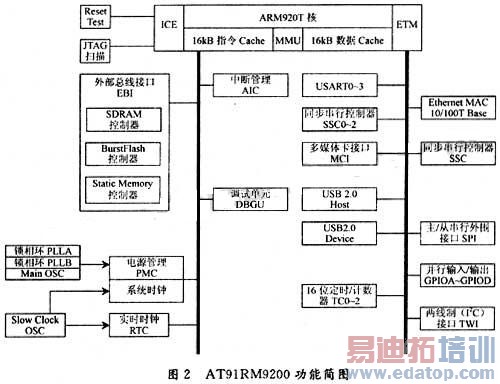

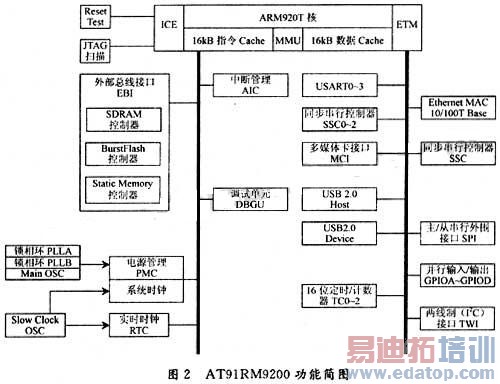

嵌入式微处理器是整个嵌入式系统的核心,AT91RM9200是Atmel公司推出的基于当前流行的ARM920T内核的一款32位RISC微控制器,工作在180MHz频率下的运算速度可达200MIPS。专门针对系统控制、通讯领域的应用。AT91RM9200芯片的功能结构如图2所示。

AT91RM9200集成了丰富的外围功能模块,满足多种应用场合,丰富适合于实时控制,可以支持实时操作系统(RTOS),为需要多功能、低成本、低功耗的计算密集型应用提供了一个单芯片级的解决方案。AT91RM9200是一款性价比极高的微处理器,经过比较选择AT91RM9200作为信号机控制板处理器。

2.1.2 控制板外围模块

控制板设计主要包括以下几个部分:

(1)电源/晶振模块:

控制主板使用12/5V两套电源供电,AT91RM9200工作于3.3/1.8V两种电压,系统其他器件尽量选择工作电压为3.3V。

AT91RM9200使用12MHz/32.768kHz两种晶振,主晶振12MHz经过芯片内倍频处理分别为ARM920T核与系统提供180MHz和60MHz的时钟频率。32.768kHz慢时钟用于AT91RM9200的启动。

(2)存储器模块。

(3)网络模块。

(4)串口模块和GPS接口:

AT91RM9200提供4个USART,分别将他们分配给RS232和RS485。控制板上预留GPS接口位置,用于未来扩展信号机无线通讯功能,GPS使用RS232同AT91RM9200通信。

(5)RTC模块:

信号机在通讯、干线或者区域协调控制中需要使用统一的时间来同步,因此设计RTC(实时时钟)用来对时。RTC可以提供可编程的实时时钟:年(含闰年)、月、日、时、分、秒、星期及一个闹钟中断,并可以在掉电后使用备用电源工作。

(6)系统总线扩展模块。

2.2 主要硬件模块电路设计

下面详细说明存储单元、网络和系统总线扩展模块的硬件设计。

2.2.1 存储器模块

本文设计的信号机需要存放嵌入式操作系统及其文件系统、应用程序和其他在运行或系统掉电后需要保存的数据;另外当系统启动后,操作系统和程序运行还需要更大的空间。AT91RM9200内部集成的ROM和RAM的容量不能够满足信号机的要求,因此设计了外存储单元来扩展存储空间,由16MB和FLASH和64MB的SDRAM组成信号机的外存储系统。

AT91RM9200的地址空间是4GB,他被划分成16个256MB的区域;

区域0为内部存储器空间;

区域1-8是给由EBI控制的外部设备(扩展的片外存储器和外接的设备)使用的,片选信号为引脚NCS0-7;

区域15是AT91RM9200集成的片内外围功能(包括系统和用户外围)使用的地址空间,当系统上电或重启时,根据引脚BMS的电平状态,系统选择是从内部ROM(BMS=1)还是从存储区域1即NCS0片选区域(BMS=0)启动。

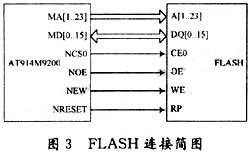

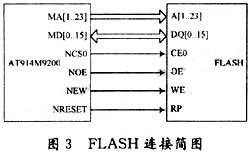

(1)本设计选用1片8M×16b数据宽度的FLASH,共16MB,作为程序代码存储器和信号机运行时的永久数据存储器。FLASH存储器在系统中主要用于存放引导程序bootloader、操作系统内核镜像和应用程序代码等,系统上电或者复位后从FLASH中运行bootloader,由bootloader初始化硬件并将操作系统拷贝到SDRAM中去执行。所以将FLASH存储器分配到AT91RM9200的BANK0(存储区域1)地址空间,即将AT91RM9200的NCSO连接到FLASH的片选端CE0。FLASH输出使能端OE接AT91RM9200的NOE;写使能端WE接AT91RM9200的NWE;模式选择端BYTE上接高电平,使FLASH工作在16位数据模块,16位模块FLASH与AT91RM9200的基本连接如图3所示。

(2)为了提高系统运行的效果,系统启动后将FLASH中代码拷贝到SDRAM中,由SDRAM作系统程序运行场所。为了发挥AT91RM9200处理器32位数据处理性能,本设计选用2片4BANK×4M×16b(32MB)SDRAM,并联组成32b的RAM,总共64MB空间,完全可以满足嵌入式操作系统及各种复杂功能的运行要求。

如图4为用2片SDRAM并联构建32位SDRAM存储系统的简图,其中一片作为高16位,另一片作为低16位,他们的数据线分别接AT91RM9200数据总线的D[16..31]和D[0..15]。SDRAM是被分配到AT91RM9200的BANK1(存储区域2)地址空间的,即将AT91RM9200的NCS1端分别接到2片DSRAM的CS片选端。因为SDRAM的第10位地址线A10还有给SDRAM预充电的作用,所以AT91RM9200提供给SDRAM专用的地址线——SDA10,来代替通用地址线MA10,并且因为32位数据读写是4字节对齐的,所以AT91RM9200的地址线MA[2..11,13,14]接SDRAM地址线A[0..9,11,12]。

2.2.2 10/100 Mb/s以太网模块

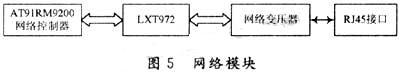

传统的RS 232和RS 485通信方式已经不适应远距离、大信息量的数据传输,而充分利用现有发达的网络系统,实现信号机联网的功能,也是智能交通发展的要求,AT91RM9200芯片本身集成有网络控制器件和28B的FIFOs栈和专用数据控制器(DMA)的接收和发送通道,硬件实现了OSI网络参考模型中介于物体层和逻辑链路层之间的介质访问MAC子层,但是没有提供物理层接口,因此需要外接一个物体层传输控制器来提供接入以太网的通道。用Intel的LXT972快速以太网PHY传输控制芯片进行数据的网络收发。

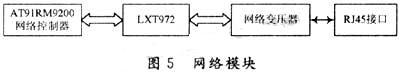

LXT972和AT91RM9200网络控制器通过介质无关接口(MII)可以很方便地连接。在LXT972和RJ45接口之间需要用网络隔离变压器来连接,网络隔离变压器起信号传输、阻抗匹配、波形修复、杂波抑制以及高电压隔离等作用,以保护系统的安全。LXT972的RX+/RX-、TX+/TX-接到网络隔离变压器上,再由变压器引出相应信号连接到RJ45接口上,网络模块以标准RJ45接口与以太网相连。其网络模块连接方式如图5所示。

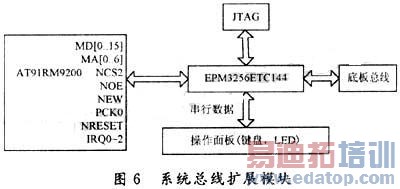

2.2.3 系统总线扩展模块

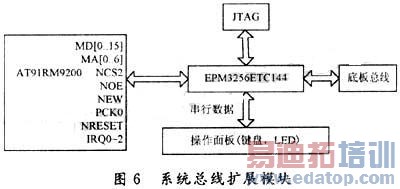

考虑到信号机的体积、靠靠性及提高信号机的模块化程度,方便设备的升级、扩展、控制板上并不直接实现控制参数输入、车流量检测等功能,信号机从控制板引出数据总线、地址总线和必要的控制信号,设计统一的系统总线,控制板通过总线来操作各个功能板,如信号灯驱动板、车辆检测板以及操作面板的键盘输入和LED显示输出,控制板和各个功能板都卡装在插槽接口。由于信号机的系统总线设计使用ISA总线标准,因此总线时序同ARM的读写时序不同,所以首先需要对ARM时序和ISA时序做转化。底板总线需要的数据、地址、读写等控制信号等都先由CPLD进行时序转换后再发送到总线上去。底板总线使用16位数据总线,7位地址总线,分配给底板总线的地址空间是AT91RM9200的BANK2区(存储区域3),片选信号端NCS2。对底板总线的读写操作由AT91RM9200的EBI(外部总线接口)来控制,嵌入式操作系统以I/O内存的方式来对他们进行管理。AT91RM9200的可编程时钟输出端PCK0用来给底板总线提供时钟信号,由CPLD对他进行分频处理,产生需要的多个时钟频率。

信号机使用操作面板的小键盘进行参数设置和方案设定,并用LED模块显示信号灯闪烁。操作面板的键盘、LED设计采用“串行”操作,即面板的键盘信号先进行“并/串”转换后,以两线同步串行方式传输到控制板的CPLD,作“串/并”转换后再发送给AT91RM9200。在操作面板自己的CPLD内,模块“8279”的工作方式,采集键盘信号,同样AT91RM9200发送给LED显示的命令数据先在CPLD中实现“并/串”转换,以两线同步串行方式,传输给操作面板,由操作面板的CPLD处理后控制LED。这种方案大大减少控制主板与操作面板之间的联线,模块化程度更好。系统总线扩展模块如图6所示。

3 嵌入式Linux系统

信号机功能比较简单时并不需要使用操作系统,而只是运行一个控制循环程序,利用中断来处理发生的事件,这样程序结构比较凌乱,难以维护或升级,功能也受限。基于工控机或PC104的信号机上一般运行通用操作系统,如Windows或DOS,前者功能虽然强大,却过于庞大,不适合信号机这样的嵌入式系统,可靠性差、容易造成死机;后者则功能较弱,已经不适合信号机功能发展的要求。

智能信号机的功能发展需要同时运行多个任务,如信号灯控制、通讯、车流量检测等等,这就要对多任务进行合理的调度;另外信号机接收和处理的信息、数据的增多,尤其是需要大量保存历史车流量数据供信号灯控制模型计算和中心查询使用,单靠表或数组来管理是复杂而效率低下的,因此文件管理也是必不可少的一项功能。

嵌入式Linux是一款优秀的嵌入式操作系统。他采用微内核体系结构,这使得核心小巧而可靠,易于ROM固化,并可模块化扩展;支持多种文件系统,如EXT2,VFAT,NTFS等;内核直接提供完善的网络支持。

本文选择功能和可靠性都很成熟的Linux-2.4.19内核版本以及针对AT91RM9200体系结构的补丁patch-2.4.19-rmk7。给标准内核源代码打上补丁后,该内核就可应用于AT91RM9200了。这就大大节省了产品开发时间,剩下的主要移植工作就是根据信号机的硬件功能编写或者修改相应的驱动程序,并在编码内核时选择需要的功能,此处不再赘述。

Linux操作系统在开发板上为应用程序运行提供了一个强大的软件平台。应用程序的开发调试有两种模式:

(1)和内核一起编译,在系统启动后运行,这种方法修改程序比较麻烦,必须重新编码内核,因此适合于简单的嵌入式系统。

(2)在宿主机上的交叉编码环境下进行编码,生成目标板上可执行的二进制文件,再通过串口和网口下载到目标板上执行,用该方法调试程序方便灵活,更适合于复杂的系统。

本文采用第二种方法来调试程序。将目标板(控制板)的调试串口和宿主机(PC机)串口相连,然后宿主机上运行minicom作为目标板的控制台。将宿主机和目标板用交叉网线连接,并设置二者的IP在同一网段。在宿主机上打开NFS(网络文件系统)服务;目标板mount宿主机的IP,如mount-o nolock 192.168.2.97://test,这样从目标板文件系统的test文件夹就可以访问到宿主机的根文件系统,宿主机上编译好的可执行文件,直接可以从目标板上看到并运行。

测试表明信号机控制板的软硬件系统都可以稳定运行,各部分功能也正常工作,证明了设计结果达到了预期的设计目标。

4 结语

本文介绍了基于AT91RM9200微处理器的智能交通机控制板的硬件设计以及嵌入式Linux软件平台。该设计方法改进了原信号机功能,增加了网络通信功能,并保留了过去的通信串口以保持兼容。整个开发板结构设计和总线接口信号都同原信号机主板一样,可以直接在现在的信号机上使用,而不用整个修改已经开发成熟的信号机,简化了开发工作。

嵌入式Linux系统也使硬件功能得到更好的管理和使用,并为信号机的软件运行提供了一个强大的平台,Linux系统下接入网络和进行文件管理更加容易安全。在Linux基础上可以更方便地开发更智能的信号灯控制算法以及其他功能。同时整个信号机系统的软硬件可靠性也得到了提高。

目前我国的城市交通控制主要还是靠道路交通信号控制机(以下简称信号机)。国内的信号机主要分为两类:一类采用8/16位单片机作为处理器,交通控制功能简单、方案单一,以RS 232或RS485为通讯方式,难以与控制中心联网以及实现区域交通协调控制等功能,不能适应现代化大路口交通控制的要求;另一类则是基于工控机或PC104,功能虽然强大,但由于工控机或PC104都是按通用计算机标准设计,并非专门针对信号机应用设计,该类信号机硬件结构复杂且很多功能并不需要,成本也高,国外的信号机(如西门子公司的2070和美国的EAGLE)开发起步早,水平高,已有各种自适应联网型信号机产品,但一般不适用于中国混合交通的实际情况,且价格昂贵,操作不方便。

信号机是一个典刑的嵌入式系统,嵌入式系统是以应用为中心来设计,对功能、性能、可靠性、成本、功耗、体积等有严格的要求,既要满足智能交通系统对信号机智能化、多功能的要求,又要最大化信号机的性价比,因此本设计选择基于ARM核的32位嵌入式RISC处理器——AT91RM9200来完成智能交通信号机控制板的硬件设计,以达到使信号机在交通系统中成为收集与处理交通流量数据、通信联网以及区域协调控制平台的设计目标。

2 信号机系统硬件设计

2.1 系统总体硬件结构

智能交通系统要求信号机可以向控制中心实时提供多种道路信息和车流量数据信息,接收控制中心的控制命令,并能够独立执行一些复杂的算法,可以根据交通流量变化实时条件路口信号灯的绿灯时间,因此考虑现有信号机的不足,根据信号机功能发展的趋势和要求,本文设计的信号机控制板具有控制参数输入、控制状态输出、控制参数保存、灯态输出控制、交通流信息(主要是车流量)实时检测与历史数据存储、多种灯态控制方案与算法模型存储、支持以太网及与手持终端设备通讯等基本功能。整个系统硬件结构如图1所示。

2.1.1 AT91RM9200微处理器介绍

嵌入式微处理器是整个嵌入式系统的核心,AT91RM9200是Atmel公司推出的基于当前流行的ARM920T内核的一款32位RISC微控制器,工作在180MHz频率下的运算速度可达200MIPS。专门针对系统控制、通讯领域的应用。AT91RM9200芯片的功能结构如图2所示。

AT91RM9200集成了丰富的外围功能模块,满足多种应用场合,丰富适合于实时控制,可以支持实时操作系统(RTOS),为需要多功能、低成本、低功耗的计算密集型应用提供了一个单芯片级的解决方案。AT91RM9200是一款性价比极高的微处理器,经过比较选择AT91RM9200作为信号机控制板处理器。

2.1.2 控制板外围模块

控制板设计主要包括以下几个部分:

(1)电源/晶振模块:

控制主板使用12/5V两套电源供电,AT91RM9200工作于3.3/1.8V两种电压,系统其他器件尽量选择工作电压为3.3V。

AT91RM9200使用12MHz/32.768kHz两种晶振,主晶振12MHz经过芯片内倍频处理分别为ARM920T核与系统提供180MHz和60MHz的时钟频率。32.768kHz慢时钟用于AT91RM9200的启动。

(2)存储器模块。

(3)网络模块。

(4)串口模块和GPS接口:

AT91RM9200提供4个USART,分别将他们分配给RS232和RS485。控制板上预留GPS接口位置,用于未来扩展信号机无线通讯功能,GPS使用RS232同AT91RM9200通信。

(5)RTC模块:

信号机在通讯、干线或者区域协调控制中需要使用统一的时间来同步,因此设计RTC(实时时钟)用来对时。RTC可以提供可编程的实时时钟:年(含闰年)、月、日、时、分、秒、星期及一个闹钟中断,并可以在掉电后使用备用电源工作。

(6)系统总线扩展模块。

2.2 主要硬件模块电路设计

下面详细说明存储单元、网络和系统总线扩展模块的硬件设计。

2.2.1 存储器模块

本文设计的信号机需要存放嵌入式操作系统及其文件系统、应用程序和其他在运行或系统掉电后需要保存的数据;另外当系统启动后,操作系统和程序运行还需要更大的空间。AT91RM9200内部集成的ROM和RAM的容量不能够满足信号机的要求,因此设计了外存储单元来扩展存储空间,由16MB和FLASH和64MB的SDRAM组成信号机的外存储系统。

AT91RM9200的地址空间是4GB,他被划分成16个256MB的区域;

区域0为内部存储器空间;

区域1-8是给由EBI控制的外部设备(扩展的片外存储器和外接的设备)使用的,片选信号为引脚NCS0-7;

区域15是AT91RM9200集成的片内外围功能(包括系统和用户外围)使用的地址空间,当系统上电或重启时,根据引脚BMS的电平状态,系统选择是从内部ROM(BMS=1)还是从存储区域1即NCS0片选区域(BMS=0)启动。

(1)本设计选用1片8M×16b数据宽度的FLASH,共16MB,作为程序代码存储器和信号机运行时的永久数据存储器。FLASH存储器在系统中主要用于存放引导程序bootloader、操作系统内核镜像和应用程序代码等,系统上电或者复位后从FLASH中运行bootloader,由bootloader初始化硬件并将操作系统拷贝到SDRAM中去执行。所以将FLASH存储器分配到AT91RM9200的BANK0(存储区域1)地址空间,即将AT91RM9200的NCSO连接到FLASH的片选端CE0。FLASH输出使能端OE接AT91RM9200的NOE;写使能端WE接AT91RM9200的NWE;模式选择端BYTE上接高电平,使FLASH工作在16位数据模块,16位模块FLASH与AT91RM9200的基本连接如图3所示。

(2)为了提高系统运行的效果,系统启动后将FLASH中代码拷贝到SDRAM中,由SDRAM作系统程序运行场所。为了发挥AT91RM9200处理器32位数据处理性能,本设计选用2片4BANK×4M×16b(32MB)SDRAM,并联组成32b的RAM,总共64MB空间,完全可以满足嵌入式操作系统及各种复杂功能的运行要求。

如图4为用2片SDRAM并联构建32位SDRAM存储系统的简图,其中一片作为高16位,另一片作为低16位,他们的数据线分别接AT91RM9200数据总线的D[16..31]和D[0..15]。SDRAM是被分配到AT91RM9200的BANK1(存储区域2)地址空间的,即将AT91RM9200的NCS1端分别接到2片DSRAM的CS片选端。因为SDRAM的第10位地址线A10还有给SDRAM预充电的作用,所以AT91RM9200提供给SDRAM专用的地址线——SDA10,来代替通用地址线MA10,并且因为32位数据读写是4字节对齐的,所以AT91RM9200的地址线MA[2..11,13,14]接SDRAM地址线A[0..9,11,12]。

2.2.2 10/100 Mb/s以太网模块

传统的RS 232和RS 485通信方式已经不适应远距离、大信息量的数据传输,而充分利用现有发达的网络系统,实现信号机联网的功能,也是智能交通发展的要求,AT91RM9200芯片本身集成有网络控制器件和28B的FIFOs栈和专用数据控制器(DMA)的接收和发送通道,硬件实现了OSI网络参考模型中介于物体层和逻辑链路层之间的介质访问MAC子层,但是没有提供物理层接口,因此需要外接一个物体层传输控制器来提供接入以太网的通道。用Intel的LXT972快速以太网PHY传输控制芯片进行数据的网络收发。

LXT972和AT91RM9200网络控制器通过介质无关接口(MII)可以很方便地连接。在LXT972和RJ45接口之间需要用网络隔离变压器来连接,网络隔离变压器起信号传输、阻抗匹配、波形修复、杂波抑制以及高电压隔离等作用,以保护系统的安全。LXT972的RX+/RX-、TX+/TX-接到网络隔离变压器上,再由变压器引出相应信号连接到RJ45接口上,网络模块以标准RJ45接口与以太网相连。其网络模块连接方式如图5所示。

2.2.3 系统总线扩展模块

考虑到信号机的体积、靠靠性及提高信号机的模块化程度,方便设备的升级、扩展、控制板上并不直接实现控制参数输入、车流量检测等功能,信号机从控制板引出数据总线、地址总线和必要的控制信号,设计统一的系统总线,控制板通过总线来操作各个功能板,如信号灯驱动板、车辆检测板以及操作面板的键盘输入和LED显示输出,控制板和各个功能板都卡装在插槽接口。由于信号机的系统总线设计使用ISA总线标准,因此总线时序同ARM的读写时序不同,所以首先需要对ARM时序和ISA时序做转化。底板总线需要的数据、地址、读写等控制信号等都先由CPLD进行时序转换后再发送到总线上去。底板总线使用16位数据总线,7位地址总线,分配给底板总线的地址空间是AT91RM9200的BANK2区(存储区域3),片选信号端NCS2。对底板总线的读写操作由AT91RM9200的EBI(外部总线接口)来控制,嵌入式操作系统以I/O内存的方式来对他们进行管理。AT91RM9200的可编程时钟输出端PCK0用来给底板总线提供时钟信号,由CPLD对他进行分频处理,产生需要的多个时钟频率。

信号机使用操作面板的小键盘进行参数设置和方案设定,并用LED模块显示信号灯闪烁。操作面板的键盘、LED设计采用“串行”操作,即面板的键盘信号先进行“并/串”转换后,以两线同步串行方式传输到控制板的CPLD,作“串/并”转换后再发送给AT91RM9200。在操作面板自己的CPLD内,模块“8279”的工作方式,采集键盘信号,同样AT91RM9200发送给LED显示的命令数据先在CPLD中实现“并/串”转换,以两线同步串行方式,传输给操作面板,由操作面板的CPLD处理后控制LED。这种方案大大减少控制主板与操作面板之间的联线,模块化程度更好。系统总线扩展模块如图6所示。

3 嵌入式Linux系统

信号机功能比较简单时并不需要使用操作系统,而只是运行一个控制循环程序,利用中断来处理发生的事件,这样程序结构比较凌乱,难以维护或升级,功能也受限。基于工控机或PC104的信号机上一般运行通用操作系统,如Windows或DOS,前者功能虽然强大,却过于庞大,不适合信号机这样的嵌入式系统,可靠性差、容易造成死机;后者则功能较弱,已经不适合信号机功能发展的要求。

智能信号机的功能发展需要同时运行多个任务,如信号灯控制、通讯、车流量检测等等,这就要对多任务进行合理的调度;另外信号机接收和处理的信息、数据的增多,尤其是需要大量保存历史车流量数据供信号灯控制模型计算和中心查询使用,单靠表或数组来管理是复杂而效率低下的,因此文件管理也是必不可少的一项功能。

嵌入式Linux是一款优秀的嵌入式操作系统。他采用微内核体系结构,这使得核心小巧而可靠,易于ROM固化,并可模块化扩展;支持多种文件系统,如EXT2,VFAT,NTFS等;内核直接提供完善的网络支持。

本文选择功能和可靠性都很成熟的Linux-2.4.19内核版本以及针对AT91RM9200体系结构的补丁patch-2.4.19-rmk7。给标准内核源代码打上补丁后,该内核就可应用于AT91RM9200了。这就大大节省了产品开发时间,剩下的主要移植工作就是根据信号机的硬件功能编写或者修改相应的驱动程序,并在编码内核时选择需要的功能,此处不再赘述。

Linux操作系统在开发板上为应用程序运行提供了一个强大的软件平台。应用程序的开发调试有两种模式:

(1)和内核一起编译,在系统启动后运行,这种方法修改程序比较麻烦,必须重新编码内核,因此适合于简单的嵌入式系统。

(2)在宿主机上的交叉编码环境下进行编码,生成目标板上可执行的二进制文件,再通过串口和网口下载到目标板上执行,用该方法调试程序方便灵活,更适合于复杂的系统。

本文采用第二种方法来调试程序。将目标板(控制板)的调试串口和宿主机(PC机)串口相连,然后宿主机上运行minicom作为目标板的控制台。将宿主机和目标板用交叉网线连接,并设置二者的IP在同一网段。在宿主机上打开NFS(网络文件系统)服务;目标板mount宿主机的IP,如mount-o nolock 192.168.2.97://test,这样从目标板文件系统的test文件夹就可以访问到宿主机的根文件系统,宿主机上编译好的可执行文件,直接可以从目标板上看到并运行。

测试表明信号机控制板的软硬件系统都可以稳定运行,各部分功能也正常工作,证明了设计结果达到了预期的设计目标。

4 结语

本文介绍了基于AT91RM9200微处理器的智能交通机控制板的硬件设计以及嵌入式Linux软件平台。该设计方法改进了原信号机功能,增加了网络通信功能,并保留了过去的通信串口以保持兼容。整个开发板结构设计和总线接口信号都同原信号机主板一样,可以直接在现在的信号机上使用,而不用整个修改已经开发成熟的信号机,简化了开发工作。

嵌入式Linux系统也使硬件功能得到更好的管理和使用,并为信号机的软件运行提供了一个强大的平台,Linux系统下接入网络和进行文件管理更加容易安全。在Linux基础上可以更方便地开发更智能的信号灯控制算法以及其他功能。同时整个信号机系统的软硬件可靠性也得到了提高。

13.56MHz NFC天线,13.56MHz RFID天线设计培训课程套装,让天线设计不再难

上一篇:BEA WebLogic RFID Edge Server产品概述

下一篇:基于nRF24E1的嵌入式2.4GHz无线接入系统