- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于AD9854的高精度高频信号发生器

录入:edatop.com 点击:

1. 引言

在现代科研、通信、电子产业中,信号发生器的精确性和稳定性往往决定了整个系统的性能与稳定与否,所以如何设计制造高品质的信号发生器成为一个很重要的课题。随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了极快的发展,它具有相对带宽很宽、频率转换时间极短、频率分辨率很高、输出相位连续、可输出宽带正交信号、可编程及全数字化结构便于集成等优越性能。而且,由于DDS是数字化高密度集成电路产品.芯片体积小、功耗低,因此可以用DDS构成高性能频率合成信号源来取代传统频率信号源产品。

本设计的应用环境兰州重离子加速器冷却储存环主环(CSRm),采用多圈注入或射频堆积加电子冷却将重离子束在横向相空间与纵向相空间进行累积。其高频系统采用铁氧体加载的同轴线性调谐腔,通过改变铁氧体磁性材料的磁导率来改变高频腔体的谐振频率。实践中是通过改变绕在其上的偏磁线圈的偏磁电流来改变其谐振频率。加速腔的频率设计范围为0.25-1.7MHz和6-14MHz。

2. 器件简介

FPGA是20世纪90年代发展起来的大规模可编程逻辑器件。随着EDA技术和微电子技术的进步,FPGA的时钟延迟可达到ns级,并且FPGA具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中,实现所谓片上系统,从而大大缩小其体积。本设计中的FPGA采用Altera公司的ACEX1K50,它具有50000个典型门数,最大系统门数199000,2880个逻辑单元,10个EAB。本例中的FPGA用于连接事例处理单元(DSP)以及外围芯片AD9854,Inter82527,串行D/A,A/D还有SDRAM的逻辑电路。更重要的是它具有微处理器的数字内核可以执行SDRAM中的用户程序。基于微软操作系统的CVI程序和CPCI机箱及主CPU板是非实时控制系统,不能完成我们所要求的任务,通常情况下采用高速嵌入式MCU或DSP处理器。我们采用的是TMS320C6713。

AD9854结合了DDS技术和高速D/A转换,其内部集成了48bit频率累加器,48bit相位累加器,正余弦波形表,高速高性能D/A转换器以及调制和控制电路,能够在单片上完成频率调制,相位调制,幅度调制和IQ正交调制等。可以产生一个频谱较纯,幅相频均可编程的正弦信号。借助于48位的相位累加器和最高300MHz的工作频率其输出波形频率的最小分辨率可以达到0.001Hz。该芯片具有单频信号产生、二进制FSK调制、“倾斜”二进制FSK调制、CHIRP信号产生,BPSK信号调制等五种基本工作模式,利用芯片所提供的功能模块可以产生多种功能扩展。利用芯片所提供的48Bit频率分辨率,在300MHz的时钟频率下,依据奈奎斯特采样定律最高可输出150MHz的模拟信号。并且频率的合成速度达到了108个/秒,满足设计要求106个/秒。

3. 系统结构及原理

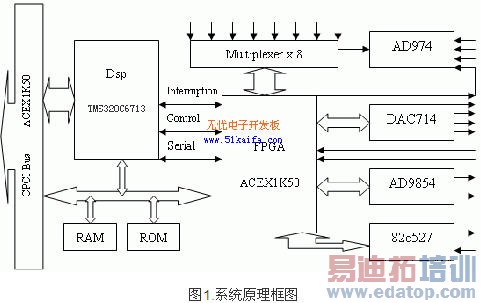

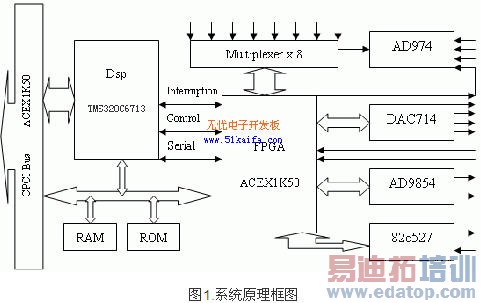

本设计中应用了许多计算机及电子方面的技术。如用FPGA实现的cPCI总线控制,Dsp负责接收事例触发并加载FPGA程序,完成系统和总线的通信,实现中断控制,整个插件集成在一块3U高度的cPCI插件上。本文主要讨论的是电路的后半部分。其中,串行ADC提供慢信号检测以及传输通道,串行ADC输出高频信号幅度调制和铁氧体的偏磁电流,Intel 82527总线控制器单元提供慢信号检测及传输通道,连接高频发射机和高频腔体的状态信号和连锁信号。本例中FPGA采用剪裁了的标准的Verilog SDRAM控制器内核以适应需求, 4Mb的SDRAM分配成2Mb的高频参数存储区和2Mb的FPGA微处理器数字内核用户程序。

4. 芯片管脚连接

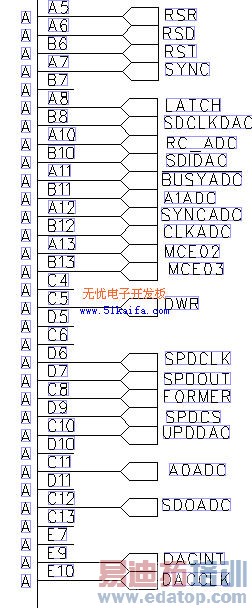

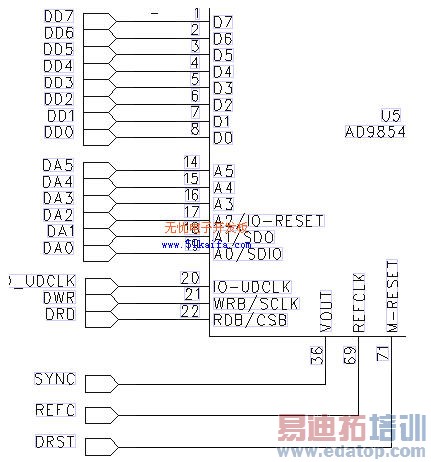

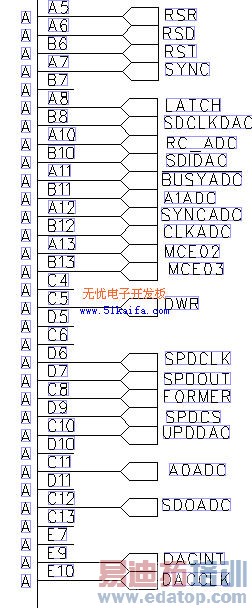

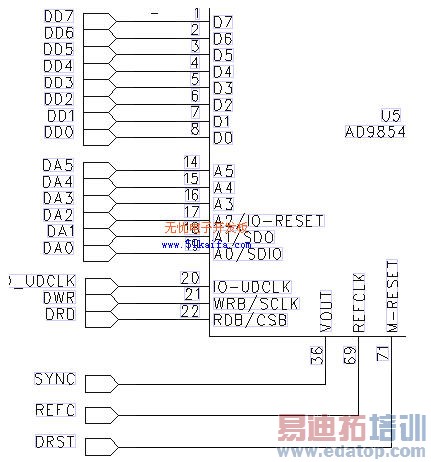

图2中给出的是ACEX1K50的管脚连接示意,其中DD0-DD7是8位的双向数据输入;DA0-DA5输入的是程序寄存器的地址,AD9854上的A0、A1、A2三个引脚还具有第二功能;I/O_UDCLK输入的是双向I/O的时钟信号,控制寄存器选择方向,默认为输出,如果是输入则在时钟上升沿将I/O端口寄存器的内容转入程序寄存器;WRB/SCLK控制将并行数据写入I/O端口缓存,当然,如果S/P SELECT管脚为逻辑低电平则进入串行编程模式,那么此时SCLK将用于串行总线关联的时钟信号;RDB/CSB是用于从编程寄存器中读取并行数据,同样的如果是串行工作模式,Chip-Select信号也将与串行总线相关联;VOUT是内部高速比较放大输出引脚。另外图2还包括了一部分与Intel82527,A/D,D/A的连接,限于篇幅就不一一叙述了,具体的内容可以参考芯片的管脚说明。

5. VHDL语言设计

在完成了硬件电路设计以后,要对FPGA进行设计,使其能够完成从DSP接收状态信息,

完成与DSP的数据交换,同时,它还要与ADC,DAC完成数据交换,并且控制CanBus控制器和AD9854,以实现信号产生控制高频腔。所以这是一个比较复杂的程序,限于篇幅,在这里仅仅给出其中一个ADC状态机设计。

……

ADC_aut : MACHINE WITH STATES (idle, p0, p1, p2, p3, p4, p5, p6);

……

CASE ADC_aut IS

WHEN idle =>IF ADC_go THEN ADC_aut = p0; ELSE ADC_aut = idle;

END IF;

-- waiting Go from PC

WHEN p0 => RC_ADC_Rg.s = vcc; ADC_aut = p1;

-- start conversion pulse

WHEN p1 => ADC_aut = p2;

WHEN p2 => ADC_aut = p3;

WHEN p3 => RC_ADC_Rg.r = vcc; IF nBusyADC THEN ADC_aut = p4; ELSE ADC_aut = p3; END IF;

-- waiting Busy End

WHEN p4 => SerEn.s = vcc; ADC_aut = p5;

-- Enable serialization

WHEN p5 => IF SerEn THEN ADC_aut = p5; ELSE ADC_aut = p6;

END IF;

-- waiting serialization End

WHEN p6 => ADC_aut = idle;

AdChan[].ena = vcc; -- Next ADC channel

ADCHlRg[].ena = vcc; -- copy to holder register

ADCHlAd[].ena = vcc;

-- end of cycle (to do programmed delay here in future)

END CASE ;

……

6. 结束语

高频信号发生器是一个非常热门也具有很大实用价值的课题,由于使用了FPGA,更好的适应了现场的修改和调试,并且模块可以具有更大的灵活性和可移植性。此设计应用于CSRm的RF Station,设计要求已经获得了实现,不仅仿真通过,而且现场应用功能正常。下一步的工作是使其和整个CSR控制系统协调工作。

本文作者创新点:本例中实现了利用FPGA和AD9854的协同工作,使得信号精度获得很大的提高并且具有控制能力,能对外围送来的慢信号进行处理并可以接收事例触发,实现跳频控制。

参考文献:

[1] 黄智伟.FPGA系统设计与实践[M].北京. 电子工业出版社:2005

[2] 陈耀和.VHDL语言设计技术[M].北京.电子工业出版社:2004

[3] 张文志,张殿胜.HIRFL-CSR主环加速腔系统设计[J].原子核物理评论,2001,3:160-163

[4] 陶益凡,唐慧强.基于AD9854的信号发生器设计[J].微计算机信息,2006,2:241-243

[5] AD9854 Data Sheet. Analog Devices[S],2004

[6] ACEX1K50 Data Sheet. Altera[S],2001

在现代科研、通信、电子产业中,信号发生器的精确性和稳定性往往决定了整个系统的性能与稳定与否,所以如何设计制造高品质的信号发生器成为一个很重要的课题。随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了极快的发展,它具有相对带宽很宽、频率转换时间极短、频率分辨率很高、输出相位连续、可输出宽带正交信号、可编程及全数字化结构便于集成等优越性能。而且,由于DDS是数字化高密度集成电路产品.芯片体积小、功耗低,因此可以用DDS构成高性能频率合成信号源来取代传统频率信号源产品。

本设计的应用环境兰州重离子加速器冷却储存环主环(CSRm),采用多圈注入或射频堆积加电子冷却将重离子束在横向相空间与纵向相空间进行累积。其高频系统采用铁氧体加载的同轴线性调谐腔,通过改变铁氧体磁性材料的磁导率来改变高频腔体的谐振频率。实践中是通过改变绕在其上的偏磁线圈的偏磁电流来改变其谐振频率。加速腔的频率设计范围为0.25-1.7MHz和6-14MHz。

2. 器件简介

FPGA是20世纪90年代发展起来的大规模可编程逻辑器件。随着EDA技术和微电子技术的进步,FPGA的时钟延迟可达到ns级,并且FPGA具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中,实现所谓片上系统,从而大大缩小其体积。本设计中的FPGA采用Altera公司的ACEX1K50,它具有50000个典型门数,最大系统门数199000,2880个逻辑单元,10个EAB。本例中的FPGA用于连接事例处理单元(DSP)以及外围芯片AD9854,Inter82527,串行D/A,A/D还有SDRAM的逻辑电路。更重要的是它具有微处理器的数字内核可以执行SDRAM中的用户程序。基于微软操作系统的CVI程序和CPCI机箱及主CPU板是非实时控制系统,不能完成我们所要求的任务,通常情况下采用高速嵌入式MCU或DSP处理器。我们采用的是TMS320C6713。

AD9854结合了DDS技术和高速D/A转换,其内部集成了48bit频率累加器,48bit相位累加器,正余弦波形表,高速高性能D/A转换器以及调制和控制电路,能够在单片上完成频率调制,相位调制,幅度调制和IQ正交调制等。可以产生一个频谱较纯,幅相频均可编程的正弦信号。借助于48位的相位累加器和最高300MHz的工作频率其输出波形频率的最小分辨率可以达到0.001Hz。该芯片具有单频信号产生、二进制FSK调制、“倾斜”二进制FSK调制、CHIRP信号产生,BPSK信号调制等五种基本工作模式,利用芯片所提供的功能模块可以产生多种功能扩展。利用芯片所提供的48Bit频率分辨率,在300MHz的时钟频率下,依据奈奎斯特采样定律最高可输出150MHz的模拟信号。并且频率的合成速度达到了108个/秒,满足设计要求106个/秒。

3. 系统结构及原理

本设计中应用了许多计算机及电子方面的技术。如用FPGA实现的cPCI总线控制,Dsp负责接收事例触发并加载FPGA程序,完成系统和总线的通信,实现中断控制,整个插件集成在一块3U高度的cPCI插件上。本文主要讨论的是电路的后半部分。其中,串行ADC提供慢信号检测以及传输通道,串行ADC输出高频信号幅度调制和铁氧体的偏磁电流,Intel 82527总线控制器单元提供慢信号检测及传输通道,连接高频发射机和高频腔体的状态信号和连锁信号。本例中FPGA采用剪裁了的标准的Verilog SDRAM控制器内核以适应需求, 4Mb的SDRAM分配成2Mb的高频参数存储区和2Mb的FPGA微处理器数字内核用户程序。

4. 芯片管脚连接

图2中给出的是ACEX1K50的管脚连接示意,其中DD0-DD7是8位的双向数据输入;DA0-DA5输入的是程序寄存器的地址,AD9854上的A0、A1、A2三个引脚还具有第二功能;I/O_UDCLK输入的是双向I/O的时钟信号,控制寄存器选择方向,默认为输出,如果是输入则在时钟上升沿将I/O端口寄存器的内容转入程序寄存器;WRB/SCLK控制将并行数据写入I/O端口缓存,当然,如果S/P SELECT管脚为逻辑低电平则进入串行编程模式,那么此时SCLK将用于串行总线关联的时钟信号;RDB/CSB是用于从编程寄存器中读取并行数据,同样的如果是串行工作模式,Chip-Select信号也将与串行总线相关联;VOUT是内部高速比较放大输出引脚。另外图2还包括了一部分与Intel82527,A/D,D/A的连接,限于篇幅就不一一叙述了,具体的内容可以参考芯片的管脚说明。

5. VHDL语言设计

在完成了硬件电路设计以后,要对FPGA进行设计,使其能够完成从DSP接收状态信息,

完成与DSP的数据交换,同时,它还要与ADC,DAC完成数据交换,并且控制CanBus控制器和AD9854,以实现信号产生控制高频腔。所以这是一个比较复杂的程序,限于篇幅,在这里仅仅给出其中一个ADC状态机设计。

……

ADC_aut : MACHINE WITH STATES (idle, p0, p1, p2, p3, p4, p5, p6);

……

CASE ADC_aut IS

WHEN idle =>IF ADC_go THEN ADC_aut = p0; ELSE ADC_aut = idle;

END IF;

-- waiting Go from PC

WHEN p0 => RC_ADC_Rg.s = vcc; ADC_aut = p1;

-- start conversion pulse

WHEN p1 => ADC_aut = p2;

WHEN p2 => ADC_aut = p3;

WHEN p3 => RC_ADC_Rg.r = vcc; IF nBusyADC THEN ADC_aut = p4; ELSE ADC_aut = p3; END IF;

-- waiting Busy End

WHEN p4 => SerEn.s = vcc; ADC_aut = p5;

-- Enable serialization

WHEN p5 => IF SerEn THEN ADC_aut = p5; ELSE ADC_aut = p6;

END IF;

-- waiting serialization End

WHEN p6 => ADC_aut = idle;

AdChan[].ena = vcc; -- Next ADC channel

ADCHlRg[].ena = vcc; -- copy to holder register

ADCHlAd[].ena = vcc;

-- end of cycle (to do programmed delay here in future)

END CASE ;

……

6. 结束语

高频信号发生器是一个非常热门也具有很大实用价值的课题,由于使用了FPGA,更好的适应了现场的修改和调试,并且模块可以具有更大的灵活性和可移植性。此设计应用于CSRm的RF Station,设计要求已经获得了实现,不仅仿真通过,而且现场应用功能正常。下一步的工作是使其和整个CSR控制系统协调工作。

本文作者创新点:本例中实现了利用FPGA和AD9854的协同工作,使得信号精度获得很大的提高并且具有控制能力,能对外围送来的慢信号进行处理并可以接收事例触发,实现跳频控制。

参考文献:

[1] 黄智伟.FPGA系统设计与实践[M].北京. 电子工业出版社:2005

[2] 陈耀和.VHDL语言设计技术[M].北京.电子工业出版社:2004

[3] 张文志,张殿胜.HIRFL-CSR主环加速腔系统设计[J].原子核物理评论,2001,3:160-163

[4] 陶益凡,唐慧强.基于AD9854的信号发生器设计[J].微计算机信息,2006,2:241-243

[5] AD9854 Data Sheet. Analog Devices[S],2004

[6] ACEX1K50 Data Sheet. Altera[S],2001