- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CMOS多频段低噪声放大器设计

电路设计

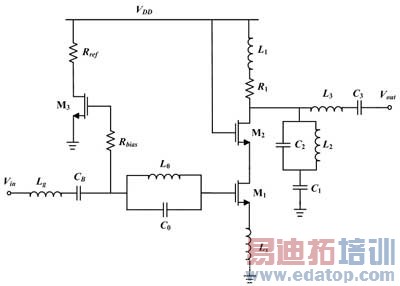

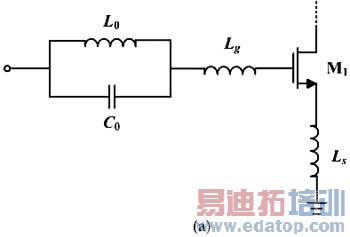

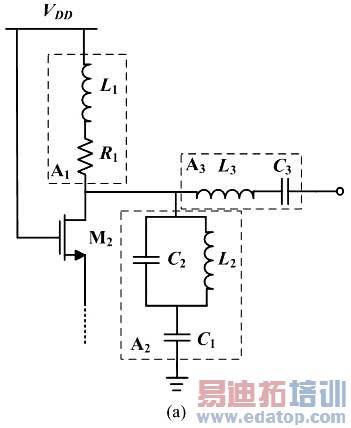

该多频带LNA总体电路如图1所示,由于1.8GHz、1.9GHz和2GHz频段很靠近,因此考虑设计一个0.9/ 1.9GHz的双频段LNA,以1.9GHz为中心频率,适当增大其带宽,使其覆盖1.8~2GHz,最终实现所需要的四频段LNA。

图1 整体电路图

1 噪声分析

高频下MOSFET的噪声主要包括漏电流噪声和栅电流噪声。对图1中带有源极电感的共源MOSFET进行噪声分析,得噪声系数为:

(1)

(1)

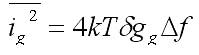

其中,Rs为信号源电阻;Zt=Zg+Zs+Zgs,Zg和Zs为连接到栅极和源极的阻抗,Zgs是连接输入管栅漏两端的阻抗,一般为1/jωCgs; ,为MOSFET的栅电流噪声,

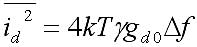

,为MOSFET的栅电流噪声, ,为漏电流噪声。

,为漏电流噪声。

在功耗限制和阻抗匹配条件下,输入级品质因数Qs≡1/ωCgsRs在3.5~5.5之间时噪声系数能达到最小值,如式(2)所示。可以看到,理论上噪声只能在一个频率点下达到最优,而不可能同时在多个频率下具有最小值。随着频率ω的增大,噪声将变大。因此对于0.9GHz和1.9GHz两个频段而言,为了达到噪声系数的平衡,选择在噪声较差的高频段1.9GHz处进行噪声匹配,由此可确定Cgs大约为 0.48pF,对应的输入管尺寸为650μm(W)×0.35μm(L)。

Fmin≈1+2.3ω/ωT( 2)

2 输入阻抗匹配

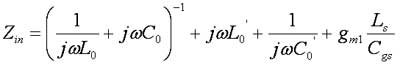

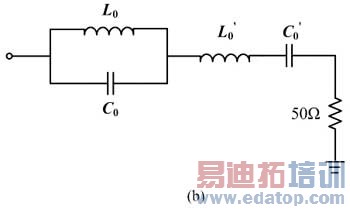

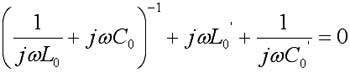

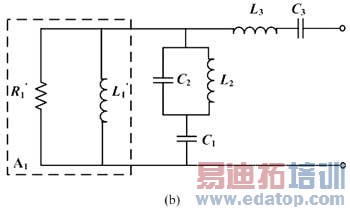

与传统的单频段LNA相比,本LNA的输入阻抗匹配网络必须同时在多个频段下匹配到50Ω。图2(a)所示为采用源端电感负反馈结构的输入阻抗匹配网络,其等效电路如图2(b)所示。其包括两个LC槽,其中,L0′=Lg+Ls,C0′=Cgs。输入阻抗可表示为:

(3)

(3)

图2(a) 输入阻抗匹配网络

图2(b) 输入阻抗匹配网络等效电路

根据阻抗匹配条件,可得出在多个频率下,输入阻抗的实部和虚部需满足以下条件:

gm1ls/Cgs=50Ω (4)

(5)

(5)

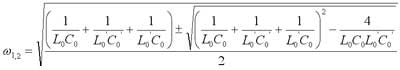

求解式(5),可得两个不同的ω值,ω1和ω2。因此,该输入网络在两个频段ω1和ω2下均可满足阻抗匹配的要求。

(6)

(6)

本设计中ω1和ω2的期望值分别为0.9GHz和1.9GHz,满足这两种频率下谐振的元件值L0、L0’、C0、C0’将不止有一组。而在实际设计所采用的工艺库中,电感值是一系列分离值,因此必须结合实际电感值进行选取。最终实现的元件值是L0=7.23nH,C0=2.5pF,Lg=10.5nH,Ls=1.14nH。

3 输出阻抗匹配

输出阻抗网络的设计与输入阻抗网络的设计类似,应考虑在多个频段下实现良好的匹配,同时输出级的设计还要满足增益的要求。图3(a)为本设计中的输出网络,其分为三部分, A1部分提供大的输出阻抗,以实现较高的增益;A2和A3共同实现双频带,A2负责阻抗下变换,将阻抗实部匹配到50Ω,A3则对虚部进行共轭匹配。

图3(a) 输出网络

图3(b) 等效输出网络

将输出网络等效为如图3(b)所示的形式,可得:

&

nbsp;(7)

&

nbsp;(7)

&

nbsp;(8)

&

nbsp;(8)

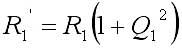

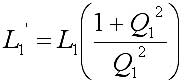

其中,Q1=ωL1/R1。

在输出网络的设计中,R1’越大,增益越大,Q1也越大,但此时R1就越小,输出网络带宽变小。由于高频段的设计是以1.9GHz为中心频率,输出网络的设计需使其具有足够的带宽覆盖1.8~2GHz,因此与L1串联的电阻R1的选取要使增益与输出网络带宽达到一定的平衡。

最终实现的元件值为L1=5.58nH,R1=15Ω,C1=1.6pF,L2=4nH,C2= 5.14pF,L3=8nH,C3=16.2pF。

仿真结果

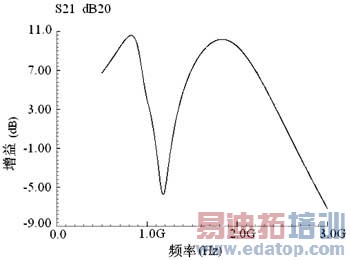

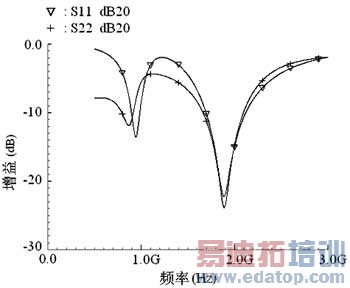

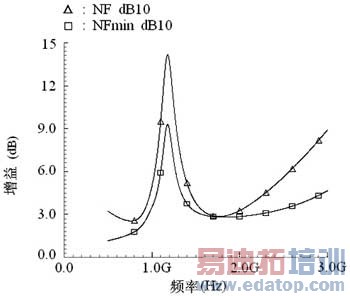

基于TSMC 0.35μm SiGe BiCMOS射频工艺库,采用Cadence的Spectre RF仿真器对所设计的多频段LNA进行仿真,得到0.9/1.8/1.9/2GHz四频段下LNA主要性能指标如图4所示。

图4(a)S21指标

图4(b)S11和S22指标

图4(c) 噪声系数NF

图4(a)为LNA的增益S21,由图可看出,在感兴趣的频段内,LNA的增益均大于10dB,且带内波动控制在0.4dB左右。图4(b)所示为LNA输入反射系数S11和输出反射系数S22,与0.9GHz处相比,1.9GHz附近的频带宽度被适当的展宽,覆盖了1.8~2GHz,所需频段处S11和S22均在-10dB以下。在本设计中为了达到高低频下噪声的平衡,考虑在高频处进行噪声匹配。图4(c)为LNA的噪声系数NF和最小噪声系数NFmin,结果表明在所希望的高频处(约1.8GHz)确实实现了噪声的最优化,同时四个频段下的噪声系数都较为平衡,均小于3.3dB。

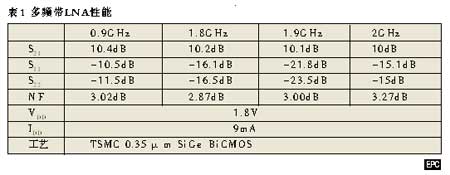

表1综合列出了各频段下的仿真性能指标。

13.56MHz NFC天线,13.56MHz RFID天线设计培训课程套装,让天线设计不再难

上一篇:通用RF器件的邻道泄漏比ACLR来源

下一篇:基于FPGA的指纹采集接口设计与实现