- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字无线电前端策略为小型蜂窝基站带来改变

小型蜂窝基站已成为无线数据泛滥的救世主,能够帮助大幅提升3G及4G无线异构网络的容量,这已不是什么秘密了。虽然让这些异构网络发挥功能的行业 标准和算法已经基本出炉,但在将小型蜂窝基站解决方案投入实际应用之前,还需要消除功耗、性能以及成本阻碍。基站制造商倾向于重点关注小型蜂窝基带片上系 统(SoC)的性能特点。基带SoC软硬件确实能对小型蜂窝解决方案性能产生重大影响,但设计的数字无线电前端部分也同样可能有明显影响,这往往被忽视。本白皮书以小型蜂窝基站的数字前端部分为重点,深入探讨在实现小型蜂窝所需性能与功耗目标时发挥重要作用的设计要素。

数字前端技术概览

蜂窝基站无线电的空中接口需要必要的数字、模拟以及RF信号处理组件,来准备供发送的调制采样,或从天线接收信号提取调制数据。

除了为模数转换器和数模转换器提供接口(LVDS/LVCMOS或JESD204A/B串行解串器)外,数字前端模块还可执行各种重要功能,其可大致分为两类:

1. 通道化与再采样功能——对任何类型的基站(微型蜂窝或宏蜂窝)、时分双工(TDD)或频分双工(FDD)、3G或4G而言,这些都是需要执行的必要信号处理功能

* 载波滤波符合频谱发射掩模及频谱泄漏要求,含根升余弦滤波(RRC)和/或线性通道均衡。

* 调谐与通道聚合/分配 — 为多载波和/或多标准基站的基础。

* 增益、相位、延迟调节与功率测量功能

2. 功率放大器(PA)线性化与RF减损校正功能——这些是真正意义上的可选项,但往往又因系统效率及成本要求而成为必需。每个模拟/RF组件在其最佳工作点 上(最佳效率、最佳动态范围、最佳噪声指标)都存在某些减损(群延迟、非线性失真、增益/相位失衡),这些减损可通过数字预/后处理进行校正。适用于减损 校正的一些主要算法包括:

* 振幅因数降低 — 用于限制信号峰值与平均功率之比,降低PA峰值功率与线性要求,进而降低系统成本

* 数字预失真 – 用于改善系统线性度,提升PA工作效率,从而可降低系统成本(CAPEX) 与运行开销(OPEX)

* I/Q失真与DC失调/LO-泄漏校正 — 是实现零IF系统架构的要件,可帮助降低系统成本,提高灵活性。

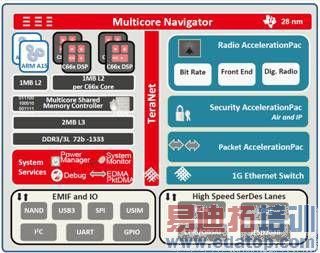

集成在新一代TI KeyStone II SoC中的业界一流DFE功能

对于优化型双模式、双频带小型蜂窝解决方案(TCI6630K2L)等基于KeySTone II架构的新一代德州仪器(TI) SoC而言,集成型数字前端无线电技术模块是重要的新增元件。以下是一些主要元件的简介。

DDUC — 多数字上/下变频转换器模块(如图1所示的DDUC)可采用单频带或多频带频率配置,支持各种信号类型(W-CDMA、LTE-5MHz、LTE- 10MHz以及LTE-20MHZ等),能够高度灵活地将BTS从单模模式3G/4G重新配置为混合模式3G/4G信号,反过来也是可以的。另外还支持高 度灵活的宽载波分离,可实现频带间及频带内载波聚合。由于异构网络(Het-Net)策略在未来几年将不断演进,所以在载波类型、信号带宽以及频带间切换 的高灵活性是极为重要的。

CFR — TI CRF模块中的业界一流算法包括各种高级特性,如支持分数峰值估算与过抵消限制功能的多级峰值抵消、根据信号频谱内容监控对CRF抵消脉冲形状的自动估算、动态阈值调整以及自动增益控制环路等。

图1:TI基带SoC(基于KeyStone II、具有集成型数字无线电功能)方框图

DPD — 使用优化Volterra模型实施PA预反转的高级数据路径是TI DPD模块的必要部件。Volterra系数通常使用各种最小平方数算法(共轭梯度Kalman等)反复改编,其可在运行在高性能浮点DSP或ARM内核 上的软件中实施,能够提供更多硬件加速选项加快迭代速度。

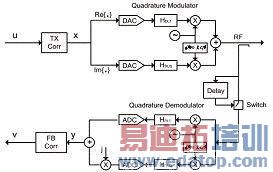

TXRX — TI TX/RX模块中实施的新颖联合I/O失真与DC偏移/LO泄漏校正技术(能够与集成型模拟/RF收发器解决方案AFE750x配合)如图2所示,可通过 在模拟域中引入相位旋转,实现发送端与接收端I/O失衡的分离。由于相位旋转对发送端与接收端I/O失衡的效果不同,因此其不但可使用高级数字算法分离失 真效果,而且还支持预补偿(在发送器上)或后补偿(在接收器上)。将实时自适应最小平方数盲算法或实时自适应最小平方数校准算法与频率相关或频率无关补偿 相搭配,可实现最佳信号SNR与发射掩模合规性。

图2:TX/RX I/Q失真综合抵消技术

除此之外,TI数字无线电模块还包括其他功能,如前端及后端自动增益控制环路(AGC) 以帮助最大限度提高数据转换器效率,降低基带处理过程中所需的动态范围;发送/接收均衡器以补偿模拟/RF滤波器固定偏差与相位失真效应;以及数字保护功 能以限制信号偏移,防止损坏PA及相关电路。这对任何BTS收发器设计来说都是深受欢迎的附加功能,只需使用低成本集成数字逻辑花销,就可实现显著的性能 提升及RF/模拟组件的成本降低。

业界一流的TI分立及集成型数据转换器、RF、时钟器件以及BB SoC现在支持 JESD204B的0子类及1子类接口,可实现理想的电路板设计,支持快速系统启动。

最后一点也非常重要,TI经过测试的生产就绪型集成平台软件不仅支持基带处理,也支持DDC/DUC、CFR与DPD库以及模拟/RF控制等数字无线电处理,可实现系统组件的快速集成以及迅速投入生产。

如图3所示,TI支持集成型数字前端技术的基带SoC(TCI6630K2L)与TI集成型无线电收发器解决方案(AFE750x)及其它TI时 钟、电源、RF器件紧密结合,再加上生产就绪型软件,可实现高性能小型蜂窝解决方案,实现可满足PoE要求的最佳功耗、低BOM成本、快速上市进程以及支 持不断演进异构网络策略的高灵活性。

图3:TI小型蜂窝系统解决方案

TI高灵活性小型蜂窝SoC支持业界一流的集成线性化解决方案,不但可在各种不同级别的小型蜂窝中实现最理想的系统成本与功耗,而且还可为满足未来发展需求提供一条易于升级的捷径。