- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高I/O数倒装芯片设计的极限尺寸测试

随着当今存储器容量增大,倒装芯片上I/O数量不断增多,倒装芯片的面积也越来越大,缺陷发生的可能性也较以前大为增加。本文通过研究底部填充材料的特性,对大型封装(指I/O数量在250个到5,770个,芯片面积从10mm2到40mm2)的设计制造工艺进行考查,以期达到减少缺陷产生的目的。

K.-F. Becker

P. Coskina

A. Schubert

德国Fraunhofer可靠性及微电子研究所

倒装芯片具有很高的互连速度和装联密度,同时体积也很小。最近柏林Fraunhofer可靠性及微电子研究所(IZM)和亚特兰大佐治亚理工学院的研究人员对倒装芯片的I/O容量和物理尺寸的极限进行了一项研究,他们根据的是SIA(半导体工业协会)对2012年存储器需求的预计情况。

为研究倒装芯片技术的极限,他们对先进热机仿真和现有的互连技术都进行了研究,得出四种基本倒装芯片,尺寸分别为10mm2、20mm2、30mm2及40mm2。针对这些设计,Fraunhofer IZM采用仿真和互连技术对尺寸大于20×20mm2倒装芯片的可行性进行了评估。

虽然有个别器件生产商已经尝试为专门应用设计高I/O数倒装芯片,但是目前还没有一个比较全面的试验报道,可以帮助了解这些大型封装的要求和限制条件。如果所有这四种芯片在封装设计和制造上都证明可行,那么40mm2大型封装不仅仅体积最大,而且在技术上也更吸引人,I/O数范围可从10mm2的250个到40mm2的5,770个。

倒装芯片封装设计和制造中的基本问题包括焊接突点上会出现的各种应力、焊接突点与底部填充材料之间的相互影响、以及底部填充缺陷如分层和孔洞等。这项研究考虑了各种底部填充材料的特性,对大封装的尺寸特性进行了测试,并设计出能避免缺陷的制造工艺。具体的可靠性研究包括如何使焊点疲劳程度最小、避免625um厚芯片的断裂及器件弯曲等等。

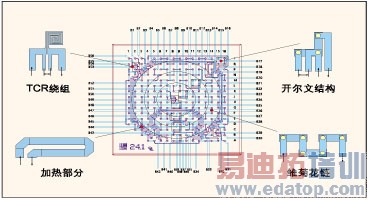

试验采用DC(菊花链)和RF(射频)测试芯片,两种芯片都从150mm(6英寸)的晶圆上切下。这些芯片包含菊花链、四点开尔文结构、温度测量TCR(阻性温度系数)绕组及加热器(图1),RF测试芯片还包括有测量电容和电感的线路结构,以及直通线和短路线等。所有RF测试结构都是通过共面线路实现的。

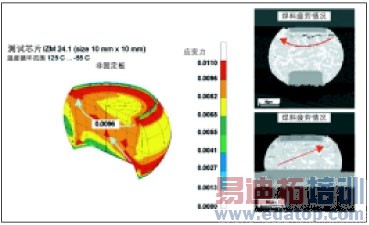

研究项目的第一步是用有限元工具对已经完成的封装进行寿命估计。计算和实际测试都采用 -55℃到+125℃温度循环范围,停留时间为5分钟,升温时间为10分钟。这主要是考察这些大型封装内焊料的疲劳度和断裂程度,因为这里电路基底和裸片之间的CTE(热膨胀系数)相差了一个数量级。

在热循环中产生的侧向运动会变得比较大,CTE差异则随着离中心越远而越大。在非底部填充倒装芯片中,裸片角落的焊接突点是最危险的,比如在40mm裸片上,角落处的焊接突点离中心很远,因而由热循环造成的应力非常大。一般来说,底部填充材料能够大大削弱侧向运动并将其中一部分转换为垂直运动,同时也可加强芯片与基底的粘结力。对底部填充倒装芯片来说,张力相对于芯片的尺寸及DNP(中点到裸片中心的距离)则没有什么关系。这些事实说明大的裸片之所以更可能会断裂,并不是因为内部张力和压力的增加,而是从统计角度看它更可能具有一种临界尺寸,在有压力的条件下会造成断裂并传播开去。

非线性有限元分析(FEA)可以预测焊接突点的受损路径,并大致估计出现故障前能经历的热循环次数。在热循环过程中,焊料易于发生弹性和塑性形变。沿着受损路径的焊料会出现疲劳,最后导致断裂,图2绘出了最外面焊接突点理论上的受损路径(红色)以及由压力造成的断裂情况。

利用FEA仿真结果的支持,系统设计人员和装配工程师一起可共同完成这种大尺寸裸片的预备、处理、组装及封装技术的开发工作。

首先是制作焊接突点,将5um厚的无电镀Ni/Au底部金属合金(UBM)做到150mm晶圆上。为了将焊膏印到这些金属合金表面,可选用120um厚的化学蚀刻不锈钢模板,而不是更贵的激光蚀刻模板。由于印制间距为500um,所以选用的孔径尺寸为350×350um。

焊接使用标准的贺利氏共晶Sn/Pb(63/37)焊膏,锡粉大小为45~75um(type 2)。回流焊按照贺利氏提供的温度曲线在氮气环境下进行,经清洗去除助焊剂之后,突点的平均高度为215um,150mm晶圆的标准偏差为5σ。

晶圆上的焊膏印刷质量由很多因素确定,如焊膏特性、模板设计、模板制造工艺及印刷机特性等等。不过印刷工艺质量可以在回流焊后的检查阶段很容易测出来,而回流焊及助焊剂清洗后焊料堆积的突点高度可使用带修订版软件的OKM 2D自动检查系统来测定。在两步式工艺中,检查系统可以测出焊接突起的直径并算出其高度。

对不同种类焊膏的最初检验过程中,最常见的缺陷是焊料遗失和桥接,原因是相邻的突点在模板印刷后连在了一起。由于焊膏连在一起,因此在回流焊过程中,焊料会从一个突点流到另一个突点,这样要不就造成突点尺寸太小,没有足够的高度与基底保持接触(焊料不足),要不造成焊料桥接(焊料太多)。其实两种缺陷印刷出来的图形是一样的,两个相邻焊点之间的连接也都能够看得到,至于回流焊后出现哪种缺陷则取决于所印刷焊膏的数量。如果某个突点的量比相邻的小,就会出现焊料遗失;如果两个的量一样,焊料就会桥接。根据所用模板样式而选用合适的焊膏(考虑锡粉的大小、助焊剂类型等等)之后,这些缺陷产生的频率可以大大减少。

第一次组装时选用的底部填充材料是标准的“硬”材料,它的杨氏模数为9.0Gpa,Tg为125℃,CTE为30ppm/K(与所用PbSn焊料的CTE相近),硅填充料的重量百分比为60%。和标准材料(68%)及快速流动环氧树脂组合相比,填料精简后可提供较低的粘性,这对于在40mm芯片下进行流动非常重要。试验中使用全自动的Asymtek旋转泵Millennium系统将液态的底部填充材料沿芯片一边进行填充,填充完后接着是低应力固化过程。先用低温进行预固化以使聚合物材料预先成型,然后按照制造商推荐的比最高使用温度更高的Tg进行后固化。

固化后使用Sonoscan 6000 C-SAM(声扫描显微镜)进行频率为100MHz的非破坏性声学缩微成像,以便观察焊接突点的大小和粘结点并进行鉴定。一般情况下,超声反射模式可用电子开关进行控制,以便只对裸片和底部填充材料之间的连接部分成像,成像范围包括局部或整个焊接突起未粘接情况、底部填充材料内的空隙、芯片钝化与底部填充材料的分层以及底部填充材料与颗粒的分离及其它缺陷等。

Fraunhofer IZM研究小组完成的工艺开发(包括晶圆焊接突点制作、将裸片置于基底上的倒装芯片组装及倒装芯片封装),其结果不仅包括工艺数据,同时也包括第一次使用可靠性评估的各种样本。

在倒装芯片设计中,普遍认为裸片角落处最外面的焊接突点承受着最大的应力,从而最容易出现缺陷。但实际并不是这样。通过仿真预测出相当准确的结果表明,即使是在最大的40mm芯片上,有缺陷的焊接突点和位置也没有关系,而是更多取决于裸片上焊接突点的绝对数量,焊接突点数量多将会增加缺陷出现的概率。

但就算是最大尺寸的裸片,如果仔细选用材料和工艺,也可以大大减少由于热引发应力而导致的破损。仔细规划还能够避免其他类型的破损,如固化的底部填充材料和裸片之间分层,以及与底部填充工艺有关的孔洞或颗粒隔离之类的缺陷。声缩微成像能够对封装的任意层面进行操作,同时也非常灵敏,不仅可探测总体缺陷,而且还可以观察到个别焊接突点的断裂或不规则现象,因此它在成像和缺陷鉴定方面非常有用。总的来看,该项研究证明了将来为满足大容量存储器要求而设计的特大型倒装芯片可以使用现有的材料和工艺来制造。

我们以后的工作计划重点将放在采用特大型裸片的倒装芯片封装制造中,包括组装工艺及与组装相关的缺陷分析,以及这类封装的热机可靠性等。