- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用24位Δ-Σ ADC高精度测量模拟小信号

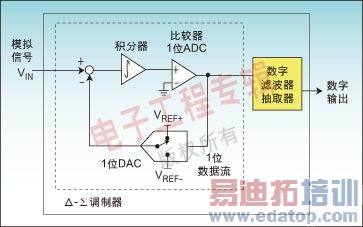

Δ-Σ ADC表面上看起来也许很复杂,但实际上它是由一系列简单的部件所构成的精确数据转换器。Δ-Σ ADC由两个主要构件组成:执行模数转换的Δ-Σ调制器和数字低通滤波器/抽取电路(decimating circuitry)。Δ-Σ调制器的基本构件(集成运算放大器、求和节点、比较器/1位ADC和1位DAC)如图1所示。调制器的电荷平衡电路强制比较器的数字输出位流来代表平均模拟输入信号。在把比较器输出回送至调制器的1位DAC的同时,还利用一个低通数字滤波器对其进行处理。这个滤波器实际上是计算0和1的数量,并去掉大量噪声,从而实现高达24位的数据转换器。

要实现更多位数的分辨率,其主要障碍是噪声。对于那些试图从热电偶、传感器或其他低电平信号源来辨别微伏级变化的设计师来说,噪声将会是一个主要的问题。背景噪声(noise floor)由所有的外部噪声和调制器周围的噪声源产生的噪声总和组成,而且背景噪声越高,检测你试图测试的模拟输入信号的真实变化就越难。

|

图1:Δ-Σ ADC由执行模数转换的Δ-Σ调制器及其后的数字滤波器和抽取器组成。 |

过采样、噪声修整、数字滤波和抽取是Δ-Σ转换器用来降低噪声并产生高分辨率输出数据的四种重要方法。假定以频率fS对一个数据转换器的输入信号采样,根据奈奎斯特定理,fS必须至少是输入频率的2倍(fIN=fS/2)。过采样是以高于输入信号频率两倍的频率对输入信号采样。一个较大的过采样比(k)将产生一个更有效的数字位流描述。组成位流的"1"或"0"越多,输入信号的数字近似就越好。图2显示了以采样率k×fS/2进行的过采样怎样让调制器将相同量的噪声扩展到更宽的频率范围上,这极大地缩小了在所关注频带中的背景噪声。过采样率每增加2倍,理想的信噪比(SNR)就提高3dB。较大的SNR意味着Δ-Σ转换器可以更好地分辨模拟输入中更小的变化。

通过用调制器控制环路中的积分器进行噪声修整,Δ-Σ转换器可以准确地测量模拟输入。积分器的噪声修整过程是将更多噪声强制推移到更高频率上,如图3所示。然后,数字低通滤波器去除噪声的高频部分,这样极大地改善了SNR。数字滤波器还可以用来极大地降低在50Hz、60Hz或其它不想要的频率上的噪声。

数字位流中总是会有一些输入信号带来的噪声。但是通过平均和滤波,Δ-Σ ADC极大地缩小了背景噪声。过采样率和内部Δ-Σ调制器的“阶数”决定噪声高低,阶数这个术语指的是积分器的数量。例如,一个3阶调制器含有3个积分器级。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:解析两项值得期待的短距离技术:RF遥控器和无线充电

下一篇:解决手机中的WiMax、蓝牙和Wi-Fi共存问题的设计挑战