- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用CMOS工艺集成通信处理架构中的射频信号链

录入:edatop.com 点击:

降低功耗

在手机设计中两个最耗电的部分就是基带处理器和射频前端。而功率放大器(PA)又消耗了射频前端中的绝大部分功率。实现低功耗的关键是使射频前端中的其他电路消耗尽可能少的功耗且不影响PA的工作。在目前所用的选择中,带译码器的GaAs开关吸纳的电流为600μA,而PIN二极管方案吸纳的电流为10mA,但在典型的射频前端应用中,UltraCMOS SP7T开关只吸纳10μA的电流。

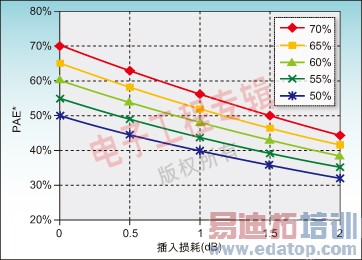

在功耗管理设计中插入损耗是另一个考虑因素。这里考虑的重点是选择不影响PA效率的前端器件。通常,GSM手机中的PA工作在高达2W的饱和功率上,它们的功率增加效率(PAE)通常约为60%。这个级别的效率对延长手机的电池来说是至关重要的。但是,如果所用的前端架构具有较高的插入损耗,PAE将会降低。图3中针对四种不同的初始PAE值,给出了有效的PAE和插入损耗(从PA到天线之间)的关系。假定前端的插入损耗为1.5dB,一个PA的PAE将从初始的60%降低至42.5%。

图3:插入损耗将引起功率放大器的功率增加效率的降低。

设计师必须继续减小元器件尺寸,改进功能,将临界的相互作用减到最小,并研发更具成本效益的电路来使手机更小,功耗更低,并瞄准4G应用。当我们展望便携式通信设备的未来时,就必须考虑新的工艺技术来实现未来的目标。幸运的是,UltraCMOS为设计师提供了所需的优异性能,能够满足所要求的标准规范,还有超高的线性度,ESD耐压,以及潜在的综合性能。

作者:Rodd Novak

市场行销副总裁

Peregrine半导体公司