- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

设计面向大众市场的千兆位级收发器

于是乎,工程师们认为可以通过无限地提高收发器的速度,来降低整个系统的成本和功耗。但是,当收发器的速度超过3Gbps后,在某些情况下会产生完全不一样的工程挑战,使得降低整个系统的成本和功耗变得十分困难。其原因十分简单:在超高速情况下,维持信号完整性的难度将越来越大,有时解决这些问题所做的额外努力要超过数据速率增加所带来的好处。

高速率带来功耗与成本挑战

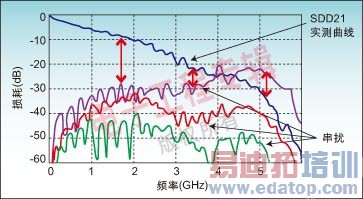

图1显示了传统背板通道的频率损耗和串扰情况。在1.6GHz时,损耗可以被合理地控制,使得速率等于或低于3.2Gbps的收发器相对具有成本效益和低功耗。

但是,在3GHz时损耗变得很高。这使得速率为6Gbps的背板式收发器需要利用许多不同的特性,你可能需要判决反馈均衡(DFE)这样的先进技术来维持信号的完整性,实现这些先进功能需要利用不同的优化特性。

这就是为什么3Gbps收发器通常每个通道只消耗不到100mW功率,而采用DFE技术的6Gbps收发器却要消耗至少两倍功耗的原因。对于需要这些先进特性的应用,这一额外的功耗开销是值得的。但如果能同时能提供低功耗3.2Gbps收发器和针对前沿应用的高性能收发器,将会凸显出竞争优势。

图1:传统背板通道的频率损耗以及串扰情况示意图。

在5GHz时,信噪比(SNR)变得很差。此时,必须使用更昂贵的材料和更复杂的制造技术来重新设计整个背板,实现10Gbps的传输条件。因此,通过背板实现10Gbps的串行传输会增加硅片面积和功耗。

前面的例子清楚地表明,工作速率等于或低于3.2Gbps的收发器处于“最佳工作点”,在大多数互连应用中,它们比并行接口和超高速收发器(6Gbps和10Gbps)具有更高的成本效益和功耗优势。这一现象导致收发器市场出现了两种不同的趋势:高带宽应用(如太比特路由器的背板互联)需要6Gbps和10Gbps的收发器,这些应用在推动性能提升的同时,对成本和功耗做出折衷;数据速率等于或低于3.2Gbps的收发器能很好地满足主流应用需求。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:关注软件设计的TD-SCDMA手机芯片组

下一篇:EDGE设计:继续获得演进的动力