- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何选择最佳的高速FPGA收发器解决方案

3. 接收机均衡

预加重是克服传输线损耗的有效手段,不过较高的驱动强度将产生电磁干扰(EMI),并且会使系统容易遭受近场的串扰。张开接收机眼图的一种替代方案或互补方案是利用接收机均衡技术。在许多应用中利用均衡技术来克服损耗并实现误码性能改善是可能的。FPGA中的接收均衡通过在接收机端放大信号中的高频分量来补偿传输损耗,而低频分量保持不变,这将有效地使信道的s-21插入损耗曲线反转,从而使得总信道的频率响应变得最平坦。均衡技术还可以与预加重技术一起使用,来补偿具有特殊挑战性的链路。

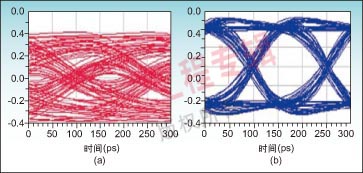

Stratix GX II收发器是完全可编程的,无论是在设计阶段还是在应用阶段,都可以在系统工作的过程中进行编程,并且能够与距离很远的设备以及在工作条件很差的环境下实现互操作性。这就使得用户可以配置均衡器使其在各种信道长度上工作。最大的均衡水平是17dB,采用4级峰值放大器来实现。这确保了所配置的系统能够实现器件速率高达6.375Gbps条件下的最佳信号完整性,而且还省去了极易传递误码、功耗大并基于DFE的外来接收机架构。图2给出了均衡器的SPICE仿真结果。

图2:(a) 到均衡器的SPICE仿真输入;(b) 来自均衡器的SPICE仿真输出。

在设计背板时需要考虑的重要因素是收发器的输出驱动能力,因为最佳信号完整性设置会由于背板版图、背板的插槽数量以及发射卡和接收卡的总体位置不同而变化。由于这种收发器优越的信号完整性性能,使得FPGA能够以6.375Gbps的速率在带有连接器的52英寸FR4背板上工作。这种可编程能力和极具鲁棒性的设计加上低功耗特性使得FPGA可工作在最具挑战性的背板、电缆、芯片或模块以及数千兆互连设备中。

4. 可编程驱动能力

某些传输线损耗可以通过增强差分输出驱动器的驱动能力以及在接收机里放大信号电平来克服。Stratix II GX架构允许设计师在4~16mA范围内选择驱动能力。实际的Vod输出驱动电压电平由终端电阻值来确定,对于50Ω的传输线来说典型的阻值范围是100Ω。

5. 功率

在所有的高密度背板应用中,功率耗散都是一个主要的问题。在这些地方空间有限,功耗和/或发热问题必须减到最小,以确保器件温度在没有风力冷却和核电站提供电源的情况下能够保持在所要求的工作范围内。

为了将收发器的功耗减到最小,采用了具有专利的PCNL输出缓冲器技术来制造Stratix II GX器件,正是由于这一高效技术使得90nm的物理媒体连接(PMA)层最大功耗仍比最具竞争力的带有收发器的65nm FPGA低20%。当在40"的FR4串行链路上工作速率到3.1875Gbps时,每四分之一收发器(四个收发器中的一个)所需的功耗为每通道125mW,而工作到6.375Gbps时的功耗则为每通道225mW。每四分之一收发器可由一到两个独立的时钟源来驱动,并具有各自独立的频率分配器。时钟和分频器的结合,能够在每四分之一收发器中支持四个不同的数据率,从而与极具竞争力的器件相比,功耗得到很大程度的降低。利用通道的基本配置能够分别判断通道上的发射机或接收机,从而进一步节省Stratix II GX收发器的功率。

6. 协议支持

先进的FPGA设计手段能够很大程度上甚至是彻底省去设计和验证FPGA与收发器件之间的数据通道所需的工作和时间。为了使收发器的性能满足特定协议标准时具有一定的余量,并能在614Mbps一直到6.375Gbps的数据速率范围内正常工作,Stratix II GX收发器经过了精心设计,因此可以提供经验证的优异性能。支持的协议标准包括PCI Express、串行数字接口(SDI)、XAUI、千兆以太网、HiGig+、Interlaken、SerialLite II、Serial RapidIO(SRIO),光纤通道以及常用的6Gbps长距离和短距离电接口(CEI-6G-LR/SR)。FPGA基本协议模式能够使系统设计适合架构师在设备的全速率范围内创建任何本土的或具有知识产权的协议。Stratix II GX系列是被证明能够满足严格的SONET/SDH OC48/STM16光抖动标准的唯一高密度FPGA系列产品,能够帮助设计师实现创新的系统和平台设计,并将FPGA的数字和协议实现功能与具有线路接口功能、背板功能、低功耗、低抖动、协议兼容收发器集成在一起。

7. 源同步和并行I/O支持

绝大多数应用要求高速源同步和并行接口提供数据平衡和流水线作业。源同步I/O(SSIO)是一个允许时钟和数据被分别(即使用LVDS信号)发送的FPGA接口。作为一个链路层接口,SSIO被用来将数据从收发器传送到系统进行处理。SSIO必须支持一个足够高的数据带宽,以确保能够向收发器连续不断地提供数据。SSIO部分包括动态相位对齐(DPA)电路,该电路将接收机时钟信号复制到变化的相位信号中,并将最近的时钟信号与进来的数据对齐。DPA能够使源同步接口支持更高的数据率,支持增强型数据通道开销,进一步提高数据率,并实现纠错、加密和线路编码。

SSTL和HSTL中具有大量可提供标准I/O连接的并行I/O,可用于高性能存储器接口、PCI接口等应用。带有收发器的FPGA所面临的挑战是如何在具有并行I/O、SSIO和FPGA数字逻辑、并且收发器所有端口在工作和被评估时同时切换的实际世界中验证标准的一致性、抗噪声能力以及鲁棒性抖动性能。

本文小结

由于要求系统支持更高的数据带宽和实现更高级的功能和特色,对高速收发器的需求正在急剧增加。通过将高速串行收发器集成到高性能、高密度的FPGA中,可以利用业已证明的全面解决方案满足许多不同的应用。为了提供全面的、可批量生产的功能,收发器技术经过了精心设计,与此同时,还提供FPGA固有的可编程方面的灵活性,从而使设计平台能够随着新协议的出现和功能的变化来支持系统的升级,而不需要改变电路板或背板的设计。对于今天的高性能应用来说,收发器的固有优点、对整套设计工具和协议支持的需求、以及一些像背板和电缆间互联、芯片间和芯片到模块间的数据传送这类应用所需的低功耗要求,都使得FPGA成为理想的器件解决方案。

作者:

Andy Turudic

高密度FPGA产品部高级经理

Altera公司