- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何选择最佳的高速FPGA收发器解决方案

用于高速设计的FPGA

将收发器集成到FPGA中,将使得设计师能够快速地解决协议和速率的变化问题,以及为了提高性能和为产品增加新功能时所做的设计修改所需的重新编程问题,而这些迫切需求的灵活性在ASIC和ASSP方案中是无法得到的。FPGA提供了一种单芯片解决方案,从而克服了多芯片解决方案中出现的互操作、布线和功率问题。位于FPGA中的收发器在克服信号完整性问题的同时能够工作在一系列不同的系统或协议环境中。

选择收发器时的考虑因素

对于获得所需的功能设计来说,收发器的选择是至关重要的。设计师必须在设计的初期阶段就分析收发器的功能和性能,并由汇聚带宽需求、协议、多媒体类型、EMC和互操作性所决定的设计准则指导选择。收发器的选择应该包括规范的符合性验证;对于像抖动、噪声、衰减和不连续性等不利条件下的免疫能力或补偿能力;以及应用中的传输媒介的类型。根据一系列器件所存在的收发器错误纪录,就不难发现将混合信号收发器集成到数字电路FPGA中仅取得了有限的成功。这就要求系统设计师在验证市场需求时特别小心,要紧盯着工艺、电压、温度、内核以及I/O口,还有硅片生产能力等各方面的工作台验证。

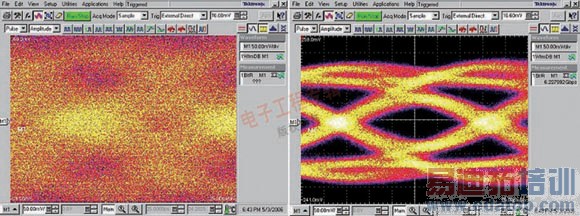

一个评估收发器的发射性能的重要工具是眼图。这是构建在一系列分层的伪随机二进制序列(PRBS)周期上的发射机波形图的量度。通过利用眼状模板,眼图可以用来显示对特定指标的符合性。如果波形没有侵占眼图模板的张开区,通常就说明它符合抖动、噪声和幅度指标。另外,为了确保采用随机性较高的PRBS序列,并将在示波器上捕获的波形采样数量减到最少,以便这些不被用来误表征较差的PRBS性能,需要一个非常谨慎的方案。

在决定生产工艺时,收发器眼图性能更是显得重要。在选择正确器件时还有如下所述的许多其它因素要考虑。

1. 信号完整性

对于芯片内部、或者芯片与模块间的通信来说,无论通信是通过背板、电缆还是同一电路板上的直接连接,带有嵌入式收发器的FPGA都是理想的选择。用串行收发器取代一个并行的高速总线可以简化系统设计。在速度高时,并行总线容易遭受干扰和串扰,使得布线相当复杂,有时甚至无法实现。而极具鲁棒性的串行收发器能简化版图设计,减少元器件和连接器数量,还能减少PCB的层数。在具有相同的总线带宽时,串行接口的功耗也比并口小。

但是收发器的更高数据率意味着非理想的有耗传输线效应会使得布线即使可能实现也变得相当困难。人们普遍应用FR4板来进行PCB设计,因为FR4的制造通常采用玻璃纤维和环氧材料,因此具有容易制造、阻燃、易钻孔、还有更重要的便宜等特点。遗憾的是,当数据率较高时,各层中的铜线开始具有典型的"趋肤效应",高频信号掠过导体的表面,减小了传导区域,因而增加了信号的衰减。FPGA设计师了解的比较少的是,在数千兆信道中传送的信号频率点,FR4介电材料本身对衰减的影响就极大,在只有几千兆的数据率上,衰减就有可能超过20dB。为了克服这些问题,带有收发器的Stratix II GX FPGA包含了发射机和接收机内部的一些功能,从而可以继续使用便宜的FR4 PCB材料。

2. 预加重

在数千兆速率时,设计师无法简单地通过放大信号来解决信号损失方面的问题,因为这将增大功耗并引起眼图的闭合。眼图的闭合可能是由发射缓冲的阻抗变坏所引起。在版图上或连接器中,反射能量的强度呈现出近端的不连续性。预加重通过加重任何信号变化后的第一个数据符号来对发射信号进行预失真处理,从而消除信道中脉冲响应的前沿过冲和后沿拖尾。

Stratix II GX收发器提供可编程的预加重功能,允许用户根据传输媒质和驱动能力来选取3个抽头中每个抽头的13级中的任意一级。最大的预加重为500%,这对张开1.25m Molex GbX背板上速率为6.25Gbps的眼图来说已经足够。图1a和图1b比较了6.375Gbps速率上对眼图开度的影响效果,该比较用的是40''迹线的Tyco FR4背板。

图1:(a) 无预加重(眼图闭合);(b) 最大预加重设置。