- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速ADC技术奠定SDR基础

信噪比

为了维持最高灵敏度,SDR必须拥有很高的信噪比,以分辨微弱信号和进行解调。无线技术标准演进到6?QAM等高阶调制机制后,对于ADC的信噪比性能要求更为严格。当天线接收输入功率很低时,ADC的信噪比(再加上本地振荡器的相位噪声)就成为限制因素,决定整个接收器的灵敏度。

SDR设计人员直到最近都还必须牺牲信噪比来提高采样频率(带宽),因为采样率高达数百MSPS的最先进ADC只有10位,信噪比则在50dBFS左右。随着ADS5463(12位/500MSPS)的出现, ADC的采样频率已大幅提高一倍(过去最高仅250MSPS),使信噪比跃增至65dBFS左右,可以实现过去无法做到的许多设计。

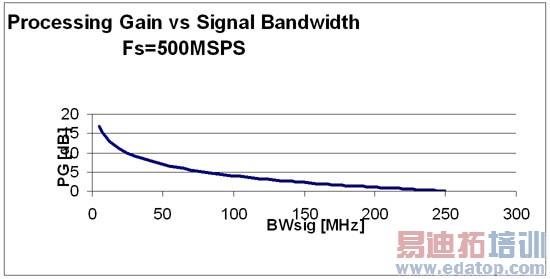

除了能够有效重建最大模拟信号带宽外,处理增益是ADC采样频率的另一项附带优点。一般而言,ADC的信噪比都是以正弦波功率与转换器在整个奈奎斯特频带(从0Hz到Fs/2,不包含直流)噪声总和的比值来计算,总噪声通常会均匀分布在奈奎斯特区域。当接收器处理该区域的某个频带信号时,数字滤波器就能大幅衰减该频带以外的噪声。假设目标信号带宽为BWSIG,ADC的采样频率为Fs,则实际的处理增益可计算如下:

图1是采样速率为500MSPS ADS5463这类超高速ADC所能提供的处理增益。SDR的数字后端可以充分利用ADC的宽带性能优点。

图1:ADC在500MSPS采样频率下的处理增益与目标信号带宽关系图。

无线接收器不断进步,最后将能直接采样射频信号。这类作业所需的ADC技术虽未出现,但相关技术突破是可预期的。值得注意的是,信号抖动最后也会对信噪比造成限制,也要列入考虑。在采样系统里,下列公式2表示信噪比与抖动之间的关系:

(2)

其中fin代表模拟输入频率,tjitter则是系统抖动的均方根值。ADC采样电路的内部抖动会以平方根和的方式,加到外部提供的转换器采样时钟。值得注意的是,信噪比的限制与实际采样频率无关,但会直接受到模拟输入频率的影响。这项基本限制将影响决定接收器中频位置时,亦即当中频提高时,简化接收器架构和滤波电路(也就是降低成本)的好处,会被ADC频率和抖动造成的限制所抵消。