- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

低功耗、双端口将解决下一代手机中处理器间通信的问题

作者:Danny Tseng, Cypress Semiconductor

Lawrence Wong、Hung Vuong, Texas Instruments

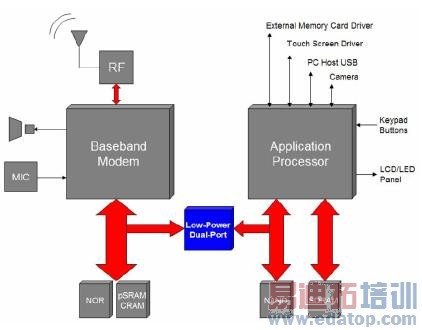

手机与其它消费电子(如PDA、MP3播放器及数字相机或摄像机等)合而为一的产品正在快速进入市场,例如Motorola ROKR和Palm Treo。在这些高性能、低功耗的设备中对电源性能的需求与日俱增,因而移动电话制造商不得不开始采用一种双处理器的架构(图1)。

在一个PDA和智能电话中,两个处理部件通常是基带处理器和应用处理器。这两个处理器各自独立工作,执行电话结构中特定的任务。基带处理器作为RF调制解调器,应用处理器则运行操作系统并完成其它多媒体功能。高级的操作系统包括Linux、Symbian和Windows CE/Mobile,通常需要一个强大的应用处理器来管理音频、视频及Wi-Fi和蓝牙等其它无线功能。

在2G和2.5G手机中,这两个处理器通过一个常见的串行接口(UART或SPI)实现互连,这些串行标准提供了一个的带宽的解决方案,通常传输速率不超过1Mbps,因此仅适合于低数据率的应用。

随着3G/3.5G网络的浮现,多媒体丰富的内容对处理器间的通信带宽提出了更高的要求,因而采用传统的串行接口将无法满足3G/3.5G应用(如实时视频、音乐、游戏等等)的需求。

近来在移动电话领域内出现了一种新的系统互连设计,即低功耗双端口存储器的解决方案。这些存储器件是专为无线手机市场设计的,可提高传输率并降低功耗。双端口具有标准存储器接口,能无缝地与所有通用基带和应用处理器连接。此外,通过和标准处理器内存接口的连接,也极大低减少了对GPIO引脚的占用。

|

1.需要实现所有3G/3.5G手机功能的双处理器架构 |

以一种数据流为例,语音和多媒体数据可以通过连接到基带处理器的天线接收进来,然后数据打包并发送给应用处理器。应用处理器既能存在文件系统中存储多媒体数据,也能实时显示/播放这些内容。基带和应用处理器之间的互连带宽在下一代3G/3.5G移动电话中可能会成为一个瓶颈。

带宽需求

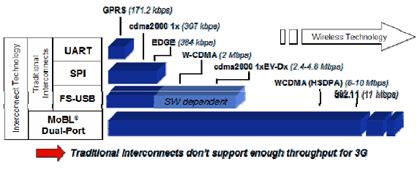

实际上在高端2G和2.5G手机设计当中双处理器结构也是得到广泛应用的。但这些网络中的数据率通常只有数百Kbps,最常见的是语音、简单的e-mail及文本信息。因此目前手机中处理器间通信(IPC)通常由两个处理器提供的SPI、UART或USB等串行接口实现。例如,GPRS和EDGE(2.5G)网络的最大数据率分别为171.2kbps和384kbps。相对而言,3G/3.5G无线标准(如CDMA2000和HSDPA WCDMA)的数据率高达10Mbps或更高,以此来支持内容丰富的多媒体信息(图2)。

|

2.各种无线标准所需的数据率 |

UART与SPI的吞吐量(约1Mbps)均不能满足3G/3.5G无线网络的带宽需求(见表)。对于目前存在于移动无线处理器中的全速USB接口,一个有趣的事实是它们提供的理论带宽为12Mbps。有人可能以为这个带宽可以满足3G/3.5G带宽的需求,然而由于协议的限制,有效带宽实际上还不到2Mbps。同时USB主机端口必须始终处于活跃状态,即使在没有数据通过互连通道传输时也不能降低功耗。此外,USB的高功耗也限制了它的IPC机制。因此,现有的串行接口中没有一种能提供3G/3.5G手机所需的数据率,另外,处理器上有限数量的USB端口也无法支持其进行IPC通信。

自从3G/3.5G无线网络标准推出以来,智能电话和PDA移动手机的设计者就一直在致力于寻找一种高效的处理器互连解决方案。许多新的设计包含了现有的串行标准,在两个处理器之间建立了多个数据传输通道。虽然看起来这是一个可行的解决方案,然而以软件来处理这类数据流非常复杂并且带来系统性的问题。由于手机设计在开发时间上的苛刻性以及面市时间在产品取得成功所占的重要地位,系统设计人员就无法在处理器间通信问题上花费更多的精力。另外一个解决方案时采用CPLD来连接两个处理器。

这种方法存在的问题体现在四个方面。首先,CPLD必须编程,因而需要更多的开发时间和资源,从而为系统设计带来不必要的复杂性。第二,CPLD通常会比其它方法占用更多的板空间,因为这种器件并非为移动应用而优化。第三,由于CPLD是一种复杂的芯片,其成本将增加开发板和其它杂项的成本,从而增加整个系统的材料成本。最后,CPLD通常比专用器件产生更大的功耗。因此,采用CPLD实现IPC非但是一个简单的方法,同时还可能为手机设计带来潜在的问题。

实现IPC的低功耗双端口

以双端口存储器作为系统互连方案近来逐渐用于手机应用当中。双端口存储器提供的高带宽数据率能满足下一代无线数据传输的需求。提供高效带宽的同时,相对于串行接口而言,双端口存储器还能通过降低功耗来延长电池寿命。

通过双端口实现的互连同时也是一个设计人员所熟悉的简单处理和应用机制。存储器接口是无缝连接到现有处理器上的标准的接口,此外无需复杂的设备驱动程序,因为这个“接口”是处理器间存储器映射的,所以能简化软件的开发并缩短产品上市时间。

硬件中断为处理器握手提供了一个简单的机制,与USB等接口相比,具有高效和最小的协议管理开销。因此能够减少不必要的存储和传输负担为处理器带来的成本。

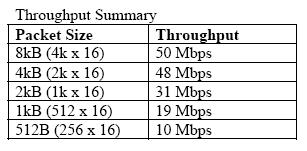

低功耗、双端口IPC的整体效率已得到深入评估,对于手机设计人员来说,评估IPC通信的实际效率比理论值更具意义。为测试实际吞吐量,Cypress和TI已开发出一个含有两个TI OMAP1710应用处理器和Cypress CYDM256B16低功耗MoBL双端口的平台。

该软件基于Symbian 8.1 EKA1 OS平台开发,通过简单的非双通道/轮流缓冲硬件中断实现握手。吞吐量基于从服务器到客户机处理器的突发数据进行计算(预设包的长度)。随硬件中断频率的变化,不同的包长度用以标记系统的实际吞吐量。基于非双通道/轮流缓冲可以改善该传输率性能指标(见表)。不过一个更保守的办法是采用简单的软件和尽量减少产生中断(图3)。

|

|

3.不同包长度对应的实际吞吐量 |

例如,采用一个全速USB和一个双端口接口分别从基带处理器到应用处理器传输一个1Mb的多媒体文件,则2Mbps的USB接口的实际时间需要0.5s,同时必须保持两个处理器各自的串行端口在数据传输期间始终激活并消耗功率。

而通过低功耗双端口接口实现的处理器互连则只需0.02s即能完成1Mb文件的传输(传输速率达48Mbps)。此外双端口和另一个处理器均能在数据传输完成之后自动进入休眠状态,从而减少了两个处理器的工作时间,使功耗降低96%。

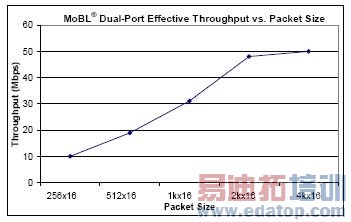

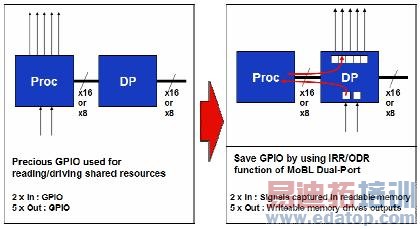

该双端口互连采用紧凑的vfBGA封装。低功耗双端口还具有输入读取与输出驱动寄存器,也能减轻处理器上GPIO的负担(图4)。

|

4.输入读取寄存器与输出驱动寄存器 |