- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

带RF输出的全数字调制器设计

软件定义无线电(SDR)终端促进了物理层功能的可编程实现。很多研究工作已经应用DSP和FPGA实现物理层的基带功能。

SDR无线电是如此定义的电台,其天线后面的某段实现了数字化。其后电台可用柔性及可配置的功能模块来实现DSP算法。随着技术的进步,数字化可以在天线后,或非常接近于天线,如此几乎所有的无线电功能都可以使用高速可编程的DSP引擎通过软件实现。

目前的无线电结合了模拟和数字构造模块。RF功能还是适合模拟电路实现,而基带功能更适合于DSP的实现。数字化前端(DFE)常用来连接RF及基带处理。DEF通常能够处理10MH左右的频率信号,常被称为数字中频(IF)。因此,重要的模拟模块留在了RF和IF之间。

数字RF收发器可扩展软件定义功能到射频频段。所有数字发射机的关键优势是高效的功率放大;数字化合并多通道信号;以及软件的可编程或可重配置性。

使用全数字发射机,整个发射机可以用DSP或FPGA实现,可以利用CMOS技术增强中的性能。除了与SDR兼容,基于DSP的RF系统可补偿RF通道的不平衡性。因此,直接在射频产生数字信号吸引了很多研究人员和工程师的兴趣。

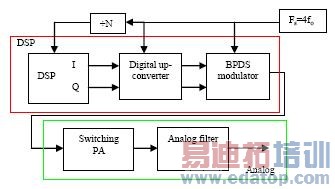

一种比较传统的方法使用带通delta-sigma调制在无线电频率上产生二进制信号。二进制信号可与开关模式功率放大器(PA)一起使用以实现比其他功放技术更高的效率(图1)。这种体系结构的限制是带通delta-sigma (BPDS)调制在中心频率的四倍处运行,达到几千兆赫。为了适应如此高的频率操作,定制的IC必须仔细设计,不具备重新编程能力。

|

采用BPDS的数字发射机 |

另外一种方式是用脉宽调制(PWM)数字合成二进制RF信号。PWM是很久以前提出的一种模拟调制,但是最近流行起来,特别是在数字音频放大应用上。D类音频PA,由PWM音频信号驱动,可达到90%以上的效率。Delta-sigma类型调制也可用于数字PWM,但与BPDS方式比较运行在较低频率。然而,delta-sigma环路倾向于比BPDS更复杂,由于其较低的过采样率和PWM有关的非线性。

测试配置使用存储在测试模式发生器中的离线计算的信号源。在本例中,设计了一个实时系统来演示使用数字PWM的RF信号数字发生器的能力。

数字RFPWM 发生器

由数字功放技术推动的数字PWM,数字信号无须依靠数模转换器(DAC)就可以直接转换成高功率模拟信号。由于全数字音频系统越来越受到关注,数字功放已经在数字音频应用上开始流行。

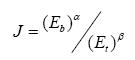

在数字PWM,脉宽以高速时钟离散化。因此,采样计数器可根据高速参考时钟产生数字PWM波形(图2)。内插器增加PCM输入的采样频率到适合PWM调制的水平。该频率经常称为脉冲重复频率(PRF)。

|

组成数字PWM系统的信号处理模块 |

正常采样器是均匀采样数字信号为基础计算正常采样信号值。显然当采用PWM时,正常采样信号基带失真远小于均匀采样。

出于实现考虑,量化需确保高速参考时钟运行在适当地频率上。例如,PCM的原始输入是44.1 kHz,16倍内插器将导致705.6 kHz的PRF。若脉宽量化到16位,高速参考时钟必须达到46-GHz。假如只需要8位量化脉宽的话,高速参考时钟可至180 MHz。因此,用适当的技术实现将比较容易。噪音成型技术,delta-sigma调制技术,常被用来抑制量化引入的基带噪声。

处理密集的模块、正常采样器、及噪音成型量化的采样频率PRF。这是该工作的主要动机——主要的信号处理算法在较低的PRF而不是RF频率上执行。

全数字RFPWM

全数字RF PWM称为正交积分噪音成型(INS),是用于量化及噪音成型模块的一种算法。其主要目标是抑制基带脉宽量化处理过程引入的噪声功率。它不同于其它在反馈环中引入非线性项的算法。不考虑INS算法的细节的话,正交INS可看成是2个独立的PWM调制器,分别用于复信号的同相(I)和正交分量(Q)。

这些脉宽调制使用以前描述过的相同体系结构。这些PWM输出的是基带信号,需要进一步和数字本机振荡器信号混合形成RF带通信号。假如基带PWM及数字本机振荡器信号都是二进制,混合操作只不过是简单的逻辑XOR操作。

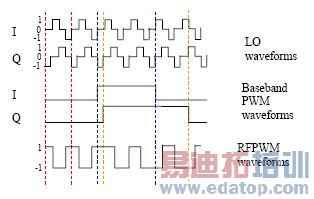

另一种简化该混频操作的方法是使数字本振的同相支路取取当0, 1, 0, -1三值,正交支路取-1, 0, 1, 0。这样,数字混频器只输出-Q, I, Q, -I 序列。当I及Q都是二进制PWM信号时,混频器的输出也将是二进制的。为了保证本振信号是2种格式中的一种,取样频率必须是4倍本振频率。来自2个数字混频器的信号组合成需要的RF信号。

对于PWM调制的信号,信号信息在脉冲宽度中承载。因为脉冲宽度定义为上升沿和下降沿之间的持续时间,在基带PWM后过度区将被保留。然而,在同相和正交本振信号之间存在90度的相位差。因此,需要特别小心的是必须确信基带PWM与他们的本振信号分别是同步的的。因为采样率设置在4倍的本振频率,相差等于1/4周期。

基带PWM同相、正交波形是分别生成的:内部引入四分之一相差来补充同相和正交本振信号之间的相差。研究基带PWM和RFPWM的定时波形,本振信号是三值格式,而组合输出RFPWM信号是二进制。此外,两个基带PWM都分别同步到其本振信号的上升沿。

|

显示了基带PWM和RFPWM的定时波形 |

此处讨论的QAM-PWM调制器使用正交PWM体系结构,由于其高计算能力需求没有选用INS算法。采用了非递归噪声成型方法。

数字PWM噪音成型

噪音成型广泛应用于过采样数据变换器上。噪音成型的目的是产生一个粗量化信号而不是精量化信号,在窄带上保持SNR性能。在数字PWM系统中,噪音成型在参考时钟频率很高时是非常必要的,脉宽精量化,在PRF是705.6 kHz使用16位而不是8位。

传统数据转换器的噪音成型滤波器已经研究的很透,大部分方法也可用在数字PWM上。但是在数字PWM上噪音成型的行为不同于传统的DAC,这是因为PWM引入了非线性。

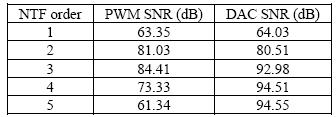

仿真模型比较了PWM与传统的DAC(图4)。数字PWM和传统的DAC使用相同的噪音成型滤波器及量化器。在该仿真器中噪音传输函数(NTF)用H(z) = (1-z-1)N规定,N取值在1到5之间。就带内噪声抑制来说该类型噪音成型滤波器不是最佳的,但足以演示PWM与传统DAC的不同。DAC的模拟部件不包含在仿真器中;仅仅考虑了所有数字噪音成型环路。下面是为仿真器所选的参数:

输入的单音信号频率 =11 kHz,基带带宽 =20 kHz,采样频率 =705.6 kHz,输入信号电平 =-6 dB,FS量化级别 =6?

对于传统的DAC,量化级别指示出最终的DAC使用的比特位数,而对PWM,则意味着高速时钟在每一个脉冲周期的取值范围(表1)。

|

PWM和传统DAC噪音整形的仿真比较 |

|

表1 |

当使用低阶NTF时,也就是,N = 1和N = 2PWM和传统DAC的信噪比测量几乎是一样的。当NTF阶数增加时,PWM的信噪比倾向不同于传统的DAC。注意:当N从2增加到3时PWM 信噪比不象传统DAC那样迅速改善;且随着N进一步由4增加到5 PWM的信噪比开始恶化。

如果NTF高频增益高量化噪音可能折回到基带。这可由PWM调制的非线性天性解释。然而,如果仅要求中等程度基带信噪比情况下,这个非线性的效果可以忽略不计。在整个仿真模型中,我们概括出为数字PWM系统设计一个非递归NTF滤波器的准则。该准则包括当滤波器输入是白噪声时,最小化基带功率与总功率的比率。滤波器参数将确保最小相位,归一化需求,其第一个系数将是1。滤波器高频增益将受限制。

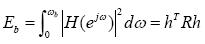

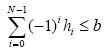

然后这些准则可用下列数学公式来阐述,假设一个N抽头FIR滤波器系数为h,这里h = (h0, h1, …, hN-1)T,基带功率可以计算出来:

|

这里R是矩阵,

|

可以使用Parseval理论计算总功率:

|

因此优化NTF应设法最小化,

|

在做优化时α 和 β参数通常作为加权因子。目标函数将在一定条件下最小化,归一化h将有界,依赖量化器级数,

|

滤波器将最小化相位,意味着滤波器零点都在单位圆内。这样高频增益将有界。

|

演示的全数字发射机指定采用10MHz的基带带宽, PRF选择100 MHz。中心频率时800 MHz;因此高速参考时钟是3.2 GHz。实现原型使用该方法设计了8抽头有限脉冲响应(FIR)NTF。

硬件原型及测量

如前所述,数字PWM的所有的信号处理算法运行在PRF频率。唯一必需的高速电路是最终的PWM波形发生器。因此,在现存FPGA器件上构造全数字QAM-PWM调节器是可行的。

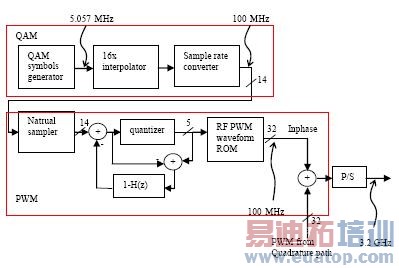

在数字QAM-PWM调制器的体系结构中,正交通道由几乎相同的体系结构模块组成(图5)。QAM调制器由符号速率5.057 MHz的QAM符号发生器、将采样比率提高到符号速率16倍的插补滤波器,以及一个将采样率转换到100 MHz PRF的转换器组成。

|

全数字RF PWM原型的体系结构图 |

数字PWM由一个正常采样器,一个噪音整形量化模块,和一个PWM波形发生器组成。正常采样算法仅由前馈数据通路构成;因此相当容易流水线化。噪音整形量化模块有反馈路径;因此尽管PRF仅为100 MHz是相当难以实现的。

FIR NTF滤波器使用变化的结构、重新定时技术及反转部分系数的符号比特(CSD)实现。本振信号与所有可能的基带PWM信号混频是预先计算并存储在ROM 中的。该ROM通过量化输出,即脉冲量化宽度来访问。来自同步和正交通道选定的RF PWM波形将在高速串行器产生1位RF信号之前组合。

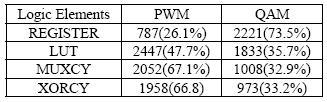

选做原型的FPGA器件是Xilinx的Virtex2pro,型号XC2VPX20-FF8?6,速率等级为7。该部件有片上多吉比特收发器,用作高速并到串转换器以产生3.2 GHz二进制信号(表2)。

|

表2 |

逻辑元素分配的结果是从Synplcity综合结果抽取的。最后的安置及布线工具报告完整QAM-PWM设计利用了18个乘法器(20%),4个RAM16 (4%),3911个基本单元(39%)。注意:括号中的数字有关于总资源的利用率。

当带通噪音电平低于信号大约45 dB时,更加进取性的噪音整形技术可实现更好的带通噪音性能。然而在这种情况下计算需求可能不利于可实现性;使用现存的FPGA将是困难的。EVM测量值小于1%,几乎与QAM输出端测量的EVM一样。