- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

4G空中接口通用的OFDMA和MIMO技术探讨

FFT的picoArray实现方案

picoChip PC102是一款高性能的多核DSP,专门针对无线做过优化。它在单个裸片上集成了300多个种类略有不同的处理器(或“阵列单元”):每个处理器均是自带存储器的传统16位哈佛结构DSP,如表1所示。

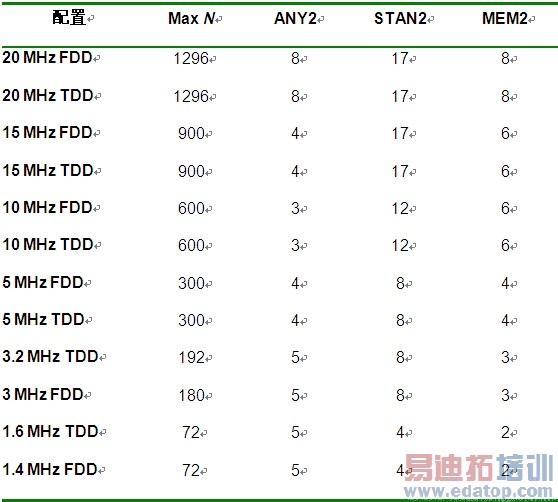

表1:PC102处理器变化和存储器分布(*FFT的最大数量受限于可用MEM类AE的数量)。

picoArray编程模型使得组装流水线结构变得非常容易,这也是实现FFT所用的方法。举例来说,每个radix-4蝶形运算包括4个复杂的乘法(注意,第4个蝶形运算只包含复杂的加法),并被映射到一个独立的处理器。每个阵列单元都是从内部总线获取输入数据,经过处理后再向流水线中的下一个DSP提供输出。由于总的吞吐量受限于最慢的阵列单元,因此理想情况下阵列单元上的每个环回都应花相同数量的周期才能实现最佳的性能。例如,如果每个阵列单元在8个周期内处理每个样值,那么最大吞吐量在160MHz时可达每秒20M个采样。

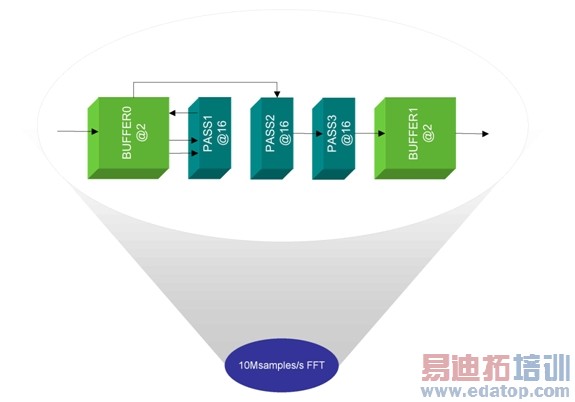

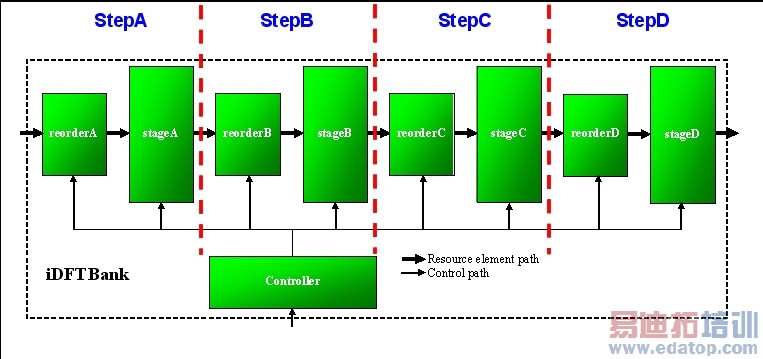

FFT实现接收16+j16、左对齐、按顺序输入的数据,提供16+j16、也按顺序的输出数据。在每个蝶形运算中会发生位增加现象,其中2个位用于加法,16个位用于复杂的乘法,这种位增加在采用就近舍入策略的40位STNA2 AE累加器中很容易管理。这种机制可以保持中间值的最佳可能精度 ,从而达到较高的输出数据信噪比。图1a显示了本实现中的单元。

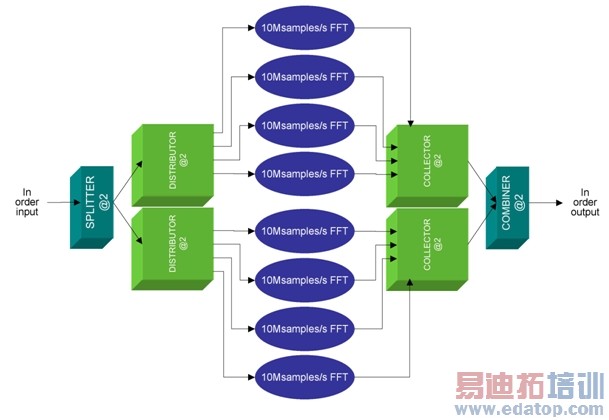

图1b:FFT内部单元;并行FFT可实现LTE上行链路要求的更高吞吐量DFT。

表2总结了PC102上的256点FFT的性能。表2给出了复杂采样速率在10MSps和80MSps之间的256点FFT所要求的资源,并给出了在PC102上能以每个速率点执行的最大FFT数量。从表中可以看出,单个10MSps FFT需要约1.5%的资源。

表2:picoArray上的OFDMA采用的256点 16+j16 FFT的资源使用。

从图1b可以看出如何通过整合“构建模块”FFT来获得更高的吞吐量--显然并行架构是非常适合的。

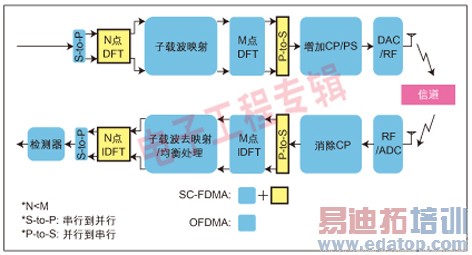

虽然目前大多数标准采用OFDM(WiFi、802.16d、Flash OFDM)或OFDMA(802.16e),但LTE选用的上行链路发送机制是最新的SC-FDMA(单载波FDMA),也称为DFT扩展OFDM。

与传统OFDMA相比,SC-FDMA的优点是信号具有更低的峰值/平均功率比(PAPR),因为它采用了固有的单载波结构。这在上行链路中尤其重要,因为在上行链路中更低的PAPR可以使移动终端在发送功效方面得到更大的好处,并进而延长电池使用时间。因此一些人士认为,SC-FDMA“集两者之大成”,即单载波的低PAPR和多载波的鲁棒性。当然,天下没有免费的午餐,这些好处的代价是增加了数字处理的复杂性,如上所述。

SC-FDMA上行链路的实现如图2所示,其中DFT位于OFDM调制器之前,这表明比标准OFDMA要多一些步骤。

图2:SC-FDMA或DFT扩展OFDM。

众所周知,如果变换点数可以分解成少量的数(素数),就可以高效地实现DFT。分解时素数越少,实现越简单。当然,经典FFT使用单个素数因子2。

LTE中的DFT预编码器尺寸取决于为指定用户的上行链路数据发送分配的子信道数量。

其中N是子载波的数量,a、b和c在 N ≤1320 条件下都大于等于0 (20MHz带宽时)。对于指定的用户,N范围可以从12个音 (a,b,c=0,即单个资源模块)到1296,总共35个不同的选择,这些音再一起经过调制形成单载波上行链路。然而,这是在手机发送器侧,因为基站接收机要处理许多用户,每个用户从这些选项中作出选择,针对所有可能的帧配置的总允许变换器数量是531、783、569。这种灵活性显然增加了接收iDFT的复杂性。

用于分解iDFT的技术是“分而治之”,主要原理与大家熟悉的FFT相同,但iDFT的长列表无法被分解成单个素数因子。相反,每个音可以被分解成长度为2、3和5的三个短iDFT。这些是iDFT的“引擎”。在本例实现中,一些iDFT已经被分解成素数因子(如4、8和9)以外的其他因子,以便将流水线级的最大数量减小至3,从而带来缩短延迟的好处。

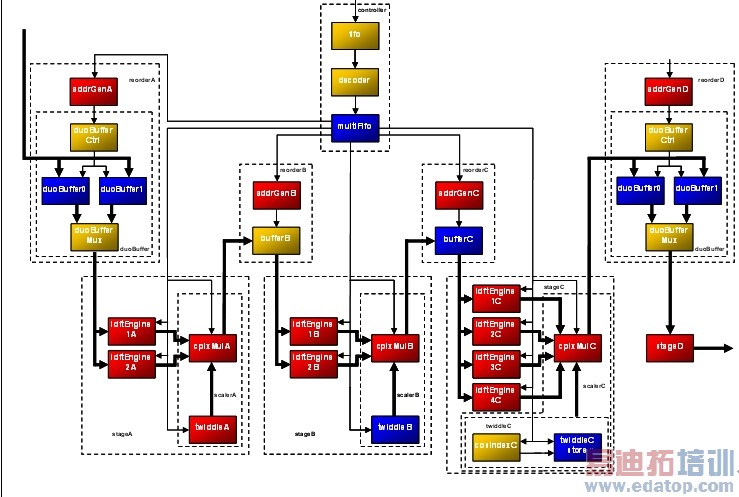

图3显示了LTE iDFT的逻辑结构,这种结构可用来在PC102/PC20x上实现20MHz的LTE eNodeB。

图3:LTE iDFT库结构。

流水线级必须能够实现所有35种可能的iDFT功能,并动态地重新配置和避免由于不同长度iDFT同时流过而造成的任何流水线危害。最简单的架构是重新排序+级缓冲对A、B和C都成为用来实现所有6个iDFT引擎的相同功能块的实例(如果计算1点iDFT就是7台引擎,即通过不变)。更优化的解决方案确认只有一级需要实现9点引擎,另外一级需要实现8点引擎,第三级需要4点引擎,加上2、3和5个引擎,因为任何iDFT长度都不需要超过一个9、8或4。

使事情复杂化的因素之一是,LTE是一个带宽可扩展的系统(简言之,TDD/FDD都是1.25MHz~20MHz)。表3列出了不同模式时的不同实现方式。虽然与FFT相比灵活性有一定的代价(见表2),但值得注意的是,这种架构在实现这些配置时效率仍然特别高:即使所需的20MHz+20MHz FDD(最坏情况)资源也仍只占PC102的10%。

表3:picoArray上可扩展iDFT的资源使用。

MIMO

MIMO是指在发送机和接收机上使用多幅天线以改善通信性能,它是所有4G系统的一个特点。

MIMO不需要增加带宽或发送功率就能显著地提高数据吞吐量和链路距离,并具有更高的频谱效率(每秒每赫兹带宽可传更多的位)和链路可靠性或空间分集性能(降低了衰落)。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:高性能低成本GPS手机的设计与实现Q&A

下一篇:照相手机浅谈(下)