- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DAB发射系统编码器的设计及实现

FPGA端主要实现IFFT(反傅立叶变换)运算,IF上变频器和数字滤波器。将PC传送来的DAB帧相位信息进行IFFT运算,完成OFDM调制,然后将调制后的基带信号经变频器变为中频信号,滤波后送给DAC模块。由于要接收来自USB模块的数据,所以FPGA上还需要一个USB接口模块。同时,在USB接口模块和IFFT模块之间需要一个内部RAM作为buffer缓冲区,IFFT运算后,数据存储到一个2048*24位的双口RAM空间,经变频和滤波后,通过DAC接口模块输出给DAC模块。IFFT运算模块,USB接口模块,上变频模块、DAC接口模块,这几个模块是通过ALTERA内嵌的NIOSII软核处理器来控制的,在FPGA上构建了一个SOPC(System On Programmable Chip)系统。FPGA设计结构如图3所示。

图3 FPGA设计结构框图

考虑到本设计所占用资源,包括逻辑单元、嵌入式存储器的多少,以达到资源充分利用,选用了ALTERA公司的Cyclone II系列FPGA EP2C20开发板,此款开发板具有512KByte的片外RAM空间,可以作为NIOS的程序存储器和USB接口的数据缓冲区,以保证数据的实时传输。FPGA各模块设计综合后占用了15000多个逻辑单元(含NIOSII模块), 占用了82%(52个M4K)的存储器位,整个系统使用65.536MHz的时钟,有效地利用了开发板的资源,结果良好。

PCB的设计

PCB的设计包含USB模块和DAC模块两部分。

(1) USB模块主要是实现PC与FPGA之间的高速通信,考虑到传输速度要达到300KB/s才能实现数据的实时传输,所以选用了FT245BL作为USB接口芯片。

(2) DAC模块是为了将数字滤波器输出的数字信号转换成模拟信号。编码器输出的是数字的中频信号,采样频率16.384MHz,带宽1.536MHz。经过DAC转成模拟信号后还需要对其放大,滤波,最后输出峰峰值为1V的DAB模拟中频信号。

本文小结

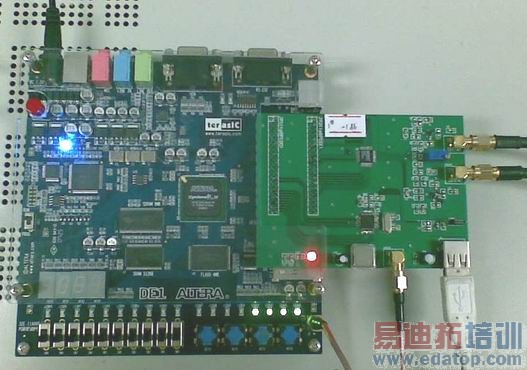

本文介绍了基于PC和FPGA的DAB发射系统编码器的设计,通过软件实现了DAB发射系统OFDM调制前的信道编码,经试验测试能够对2.048Mb/s的ETI数据流进行实时的信道编码,同时通过USB接口传输给FPGA上OFDM模块的数据率可达到320KB/s,满足了实时的要求。最后,DAC模块输出的模拟信号经过SMA连接头送入DAB发射机。图4为DAB发射系统编码器实物图。事实证明,将信道编码部分放在PC端是简单有效的实现办法,用FPGA来实现信道编码部分将是下一步的工作。

图4 DAB发射系统编码器实物图

作者:麦胤

张红升

重庆邮电大学光电工程学院

陆明莹

总经理

西安西芯微电子有限公司

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:如何为多种无线标准设计可编程基带设备

下一篇:解析低功耗无线传感器网络标准