- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

优化DBDM手机处理器之间的通信

解决处理器间连接问题的潜在方案之一是使用多端口互连,这也是目前许多DBDM架构使用的方法。在这种架构中,缓存式多端口器件作为两个CPU之间的互连桥梁,可以在两者间实现高速数据传输,并有助于在处理器间通信(IPC)时降低功耗。

速度

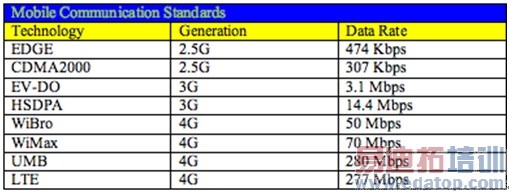

使用多端口互连的最明显好处是速度。由于存取时间快至40ns,双端口存储器最高可支持400Mbps。这不仅为HSPA功能手机提供了足够的支持,而且为未来吞吐量需求的持续增长(如LTE)奠定了基础。随着手机复杂性的提高,处理器间传输的数据量增加是不可避免的。通过多端口互连,手机设计师将不再面对处理器间通信的瓶颈问题。

功耗

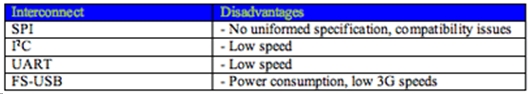

除了高速外,低功耗是DBDM手机的另一个关键要求。如果在IPC过程中要求两个基带处理器一直保持工作(比如在SPI、UART、I2C或USB互连情况下),电池寿命将大打折扣。除此之外,处理器之间的主动通信需要耗用每个处理器的专门资源,因此会降低它们的性能。

多端口解决方案可以实现处理器之间的被动通信。一个处理器可以在需要时写入到多端口互连,然后进入睡眠模式。另外一个基带处理器则可以根据自身情况随时访问这些数据。由于多端口互连起着缓存的作用,接收处理器可以一直处于睡眠模式,直到从多端口互连收到中断指令才激活。

让我们通过具体例子比较一下多端口IPC解决方案和基于全速USB的IPC方案。有效吞吐量为6Mbps的全速USB方案需要花80秒的时间传输60MB数据或10首MP3歌曲。而使用多端口互连方案以100Mbps的速度(假定为有效吞吐量)传输同样大小的数据只需要5秒。

带1.2V内核的典型基带处理器正常功耗是120mW,睡眠模式时为0.24mW。如果两个处理器在80秒传输时间内都处于工作状态,USB方案将消耗5.33mWH的电流。在多端口方案中,数据传输期间只有一个处理器工作,因此多端口互连耦合(27mW)和处理器一起消耗的总电池能量仅为0.743mWH,相当于在单个IPC场合节省了约85%的功率,这在越来越多的人通过手机下载音乐、照片、收发电子邮件和浏览互联网的今天具有极大的价值。

灵活性

互连缓存的另外一个优点是用多端口器件实现IPC不需要软件驱动程序。因此手机制造商不需要对总体软件IPC架构作大的改动就能轻松地为不同地区推出不同型号的手机。这还为制造商带来了更大的灵活性,他们可以使用在不同处理器上运行的不同操作系统,并根据系统需要而不是IPC限制来选取处理器。

单芯片解决方案

最近推出的单芯片解决方案包含了选定的GSM和CDMA频段,非常值得关注。在这种方案中,由于单芯片需要适应所有必需的功能,因此很多时候都会牺牲一定的特性和性能。而且这些处理器比较新,还没有经过市场的考验。大多数制造商仍喜欢使用经试验和测试过的解决方案,而且通常不愿意在性能要求方面作出太大的妥协。双处理器架构将成为满足不断提高的网络速度和性能要求的有力竞争者。

本文小结

随着HSPA功能手机的推出以及视频和数据内容质量的改进,许多处理器间通信架构也日趋完美。传统的互连架构已无法支持与基带处理器功能和未来移动通信标准匹配的数据吞吐量。一些手机设计师已经开始意识到这个越来越迫切的问题,并在DBDM手机设计中开始使用低功率多端口互连方案。多端口互连不仅能够满足当今手机所需的高带宽和低功耗要求,而且向设计师提供了更大的灵活性,可以帮助他们以更低的成本和更快的上市时间推出更高质量的手机。

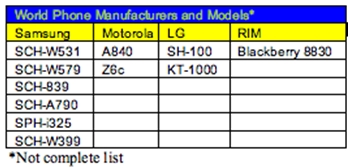

表1:“全球手机”制造商和及手机型号。

表2:蜂窝通信标准及相应传输速率。

表3:几种手机处理器常有的通信接口及其缺点。

作者:Ming Hoong Chong

产品副经理

数据通信事业部

赛普拉斯半导体公司