- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用Cortex-R7和XC4000处理器设计LTE-Advanced调制解调器架构

双核Cortex处理器具有本地存储器,专用于加速第二层处理的实时功能以及第一层的控制功能,利用低延迟本地存储器,比如第一层和第二层缓存,可以最大限度地减少片外存储器访问,从而显著降低总体系统功耗。特别需要注意,每个内核具有TCM存储器,可以存储时间关键中断程序,从而使它们以确定性方式执行,这在应对LTE-Advanced低延迟系统定时挑战方面是非常重要的。两个内核均拥有自己的本地第一层指令缓存,ARM还提供第一层数据缓存,再次帮助提高各个内核的执行效率,使得系统能够更快地执行程序,从而更快地返回节能模式,通过最大限度地减少成本昂贵的片外存储器访问,使得各个内核更长时间地停留在节能模式,降低总体系统功耗。

在设计SoC时,设计人员必须特别注意存储器和总线架构,以避免因设计瓶颈而导致性能方面付出巨大代价,或者,通过增加规格不合适的片上存储器,既增加芯片面积,又提高了功耗,从而使得解决方案变得昂贵。Cortex-R7处理器低延迟外设端口(LLPP)用于为计算第二/三层卸载功能,比如密码和健壮报头压缩(RoHC)提供了优化接口,这两层都需要进行仔细的架构考虑,从而提供优化性能而不影响总体系统吞吐量。

通过仔细设计,利用各种片上和片外存储器,ARM和CEVA架构可以实现性能/成本/功率的有效平衡。本地AXI总线为低延迟紧耦合存储器提供了专门访问,可用于不能容忍高速缓存缺失/可变延迟的时间关键的确定性任务。主要的AXI总线提供了对系统闪存和SDRAM构件的访问,SDRAM构件通常是片外资源,但常常通过叠片集成到基带封装内,以节省PCB面积。闪存用于启动整个系统,在启动期间,Cortex-R7将配置CEVA子系统并初始化所有的存储器。

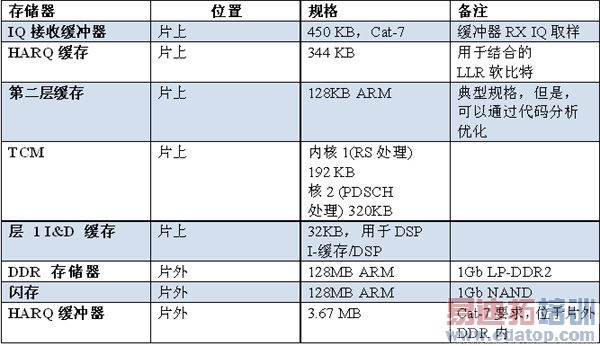

表2列出了在LTE-Advanced调制解调器设计预期看到的典型存储器类型总结。从表中可以看出,H-ARQ缓存和IQ接收缓冲器所占的基带芯片面积不断增大。H-ARQ缓冲器用于重组接收的数据,由于数据以软比特形式存储(对数似然比是“1”或“0”,而不是二进制位),因而存储器要求快速扩展。至于缩小H-ARQ缓冲器体积的压缩技术,还考虑将缓冲器放置在片外SDRAM中,以缩减数字基带芯片的尺寸/成本。CEVA和ARM IP的结合有助于最大限度地缩短通过系统的处理延迟时间,还可以提供优化的总线互连,帮助实现此类存储器优化。

表2:系统存储器要求

【分页导航】

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:数字技术能否掌控4G基础设施?

下一篇:如何进行滤波器设计软件选择