- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

选择适合高频应用的高速ADC

单内核ADC

对于在L频段应用中使用的ADC来说,有两个关键指标很重要,即频谱纯度和本底噪声。

频谱纯度:

真正的单内核架构具有很大的优势,因为它不需要内部交替就能达到1.5GS/s的更新速率。因此在扩展温度范围内工作之前或工作期间都无需校准。(交替型ADC的一个特点是具有显著的交替脉冲。偏移失配将产生一个固定频率的脉冲。然而,增益和相位失配将产生取决于输入信号频率的杂散频率。事实上,使用内部交替的ADC经常要求校准来避免由于增益、偏移和采样孔径延时的失配而引起的无杂散动态范围性能劣化。

从图2所示的频谱纯度图可以看到单内核的优势。频率的选择要使主信号及其谐波在FFT图中紧靠在一起。这样可以使频谱其它部分自由地显示与任何其它非信号相关的杂散信号,比如时钟脉冲。交替式ADC也许能很好地在这个区域显示脉冲,但我们可以看到,单内核具有无杂散区和90dBc的频谱纯度。

单内核架构在延时方面也有优势。例如,EV12AS200的延时可以低至3个时钟周期,这在电子战争和跟踪系统等应用中非常有用。

图2:EV12AS200的频谱纯度图。

本底噪声:

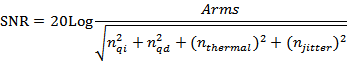

高带宽ADC的信噪比背后的因子可以由下列公式确定:

其中,nqi是理想量化噪声q/√12,nqd是与理想(DNL)的偏差。nthermal是热白噪声,njitter是总的抖动值,由内部ADC抖动和外部时钟抖动组成。

如果内部时钟抖动大约为100fs rms,这意味着外部时钟的选择应实现至少具有这个抖动值的系统,理想情况下更小的抖动可以实现最佳的性能。下表给出了根据EV12AS200 ADC指标计算噪声性能的例子。

表1:典型的本底噪声计算。

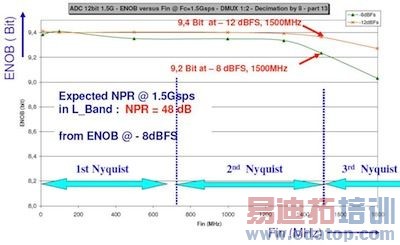

L频段应用中另外一个重要的考虑因素是,一直到第二奈奎斯特区的末端性能都应保持稳定。这也暗示带宽应覆盖这个区域,而且诸如SFDR、三阶互调指数和有效位数(ENOB)等性能参数应保持平坦(见图3)。

图3:EV12AS200的有效位数值。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:2012,谁将成为物联网应用突破点?

下一篇:如何简化向多核的迁移的基本指导