- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

低噪声、高线性度的3.5GHz LNA设计

片外电路

匹配、射频去耦和偏置功能总共需要12个片外元件,因为这些功能无法集成在芯片上(表1)。

表1:LNA评估电路的物料清单。

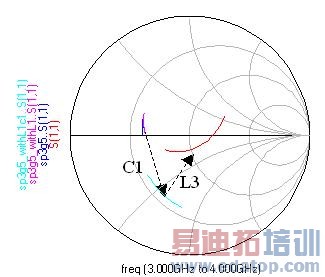

C3、C6和L1提供栅极偏置的射频去耦。C1-L3 L网络将器件S11转换为Z0,如图2所示。输入的中频带有意偏移完美的匹配状态,以便能够"环绕"Smith图中心以获得更宽带宽。高通拓扑结构可以复现低频(LF)工作。

图2:仿真得到的输入匹配轨迹。

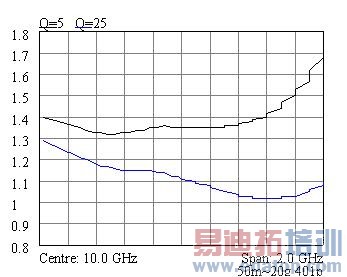

器件ZOUT在f0时已经接近50Ω,因此不需要进一步匹配。C2和L2则分别用作隔直器和扼流圈。它们还隐含有高通特性,可进一步增强LF稳定性。在第一次设计迭代过程中,L2用的是一个0402绕线电感,这将在最低频点(11GHz)形成0.94的Rollett稳定系数(k)。当L2在后来的原型中用多层0402电感代替时,这个最低系数k在10GHz可轻松的提高到1.2(见图3)。我们认为这个多层电感在10GHz点具有更低的Q(品质因数)是稳定性提高的根本原因。图3中的仿真结果支持这一推测,即通过选择更低Q值的L2可以提高稳定系数k。

图3:仿真得到的k与频率的关系:L2降低Q值的函数。10GHz时,将QUL从25降低至5可以提高稳定系数k。

为L1-L3选择的芯片电感应具有比f0更高的自谐振频率(SRF)。如此谨慎的做法可以确保3.5GHz处电感的运转状态具有可预测性。

由于输出和输入引脚的偏置电压来自同一电源(Vdd),因此,一部分输出信号可能通过传导的方式沿着公共的直流通路返回到输入端。输出和输入信号的相量叠加可能形成增益纹波,甚至低于f0的振荡。为了避免电源上发生意外的输出至输入反馈,需要使用去耦电容C3-C6将交流信号旁路到地。小电容和大电容的组合使用可以在更宽的频谱上实现有害信号的抑制。

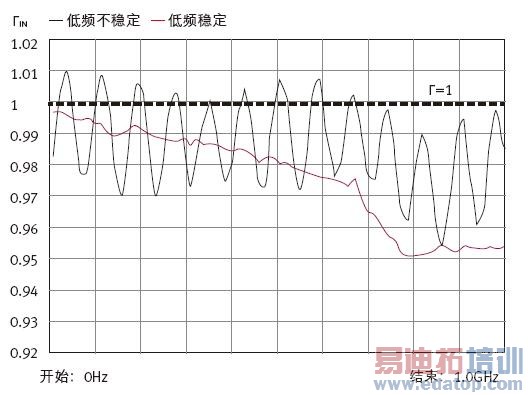

尽管输入匹配电路具有高通响应特性,但其有限的带外抑制允许一定程度的低频信号渗入。由于FET栅极在低频时接近开路,所以信号将被反射回源极。由于入射和反射的输入信号在频率范围内存在相位变化,因此它们的矢量叠加将在输入反射系数(ΓIN)上产生纹波,如图4所示。在纹波尖峰超过单位1的频率点,放大器可能会变得不稳定。由此可以知道,稳定性判据k在受影响的频率处也将小于1。由R2和C6组成的解决方案给反射信号提供了电阻端接,因此可以降低f0以下的纹波。

图4:在增加R2-C6低频端接网络之前和之后测得的输入反射系数。

为了在时域双工(TDD)模式下切换LNA,RBIAS的Vdd端可以被重新连接到0/5V控制逻辑。切换时间受RBIAS和C6的大时间常数(τ=RBIAS·C6)限制。为了实现更快的导通,C6可以减小到与C3相同的值。在此评估板上,C6值为10pF时,测得的导通时间约为0.6μs。

面积为21.5x18mm2的PCB在10mil的Rogers RO4350材料上使用了带共面地的微带线。这种价格适中的基板具有适度的射频性能,并且与FR4制造工艺兼容。由于RO4350 PCB本身较薄而太柔软,因此需要在其地平面侧粘贴一块1.2mm厚的FR4附加层进行加固,使PCB叠层足够厚(1.45mm),以适合使用标准边缘安装(edge-launch)射频连接器的滑合座。

MMIC底部的中央板和引脚4必须使用尽可能短的路线连接到射频地,以尽量减小有害的寄生效应。如果在MMIC和PCB地平面之间存在明显的寄生电感,可能出现包括增益下降和频率大于10GHz的振荡等问题。在MMIC下方直接放置4个过孔就可以实现到底部地平面的连接。根据良好的射频使用习惯,所有未用的MMIC引脚也都连接到地。

元件和PCB建模

为了尽量减少甚至避免实际的调整,在建立原型之前需要通过仿真设计片外电路。预测潜在问题(如带外不稳定性)还有助于避免将错误的PCB版图提交给制造部门。

为了便于匹配电路的设计,需要通过测量处于典型偏置条件下的定制设计夹具上的物理器件获得MMIC散射参数(s2p)。这种特征化夹具使用与原型LNA相同的PCB材料(10mil RO4350)。在利用穿透反射线(RTL)技术从原始数据中除去夹具效应后,生成的s2p数据就反映了器件及其PCB封装外形(即器件下方的安装焊盘和基板)。然后把s2p文件导入安杰伦科技的ADS2006A软件用于电路仿真。

在第一次仿真迭代过程中,可以采用简化的等效电路对片外元件进行建模。虽然制造商提供的s2p文件可以用于构建这些RLC无源器件的模型,但它们缺乏随时修改元件值的便利性,可能减慢仿真器中的调谐过程。另外,电容制造商提供的s2p数据在有效性方面有严格的限制,因为它沿着芯片长轴只有一个参考面,所以其只对于并联电容才是准确的。因为串联在射频通路中的电容是真正的双端口器件,需要两个参考平面,即一个端子需要一个参考平面,所以这种数据无法准确地表述这种电容。

通过直观地选择最重要的寄生元件,可以创建简化的RLC元件等效电路,正如Rhea描述的那样。由2个或3个元件的等效电路组成的这些元件模型只能解决基频谐振,而现实世界的无源元件具有多种更高的谐振频率。更精确的建模技术(如基于测量的模型)可以覆盖多种更高的谐振频率,但是要求额外的测量和计算机优化来开发。为了设计LNA阻抗匹配电路,可以容忍简单模型的频率限制,因为我们主要是对f0周围的频率范围感兴趣。值得注意的是,制造商提供的许多s2p文件也是频率受限的。

电感模型使用了最接近f0的频率点(通常是1.7GHz或1.8GHz,具体取决于制造商,这在数据手册中可以找到)规定的QUL典型值,然后可以使用Q∝√f关系外推到3.5GHz以上。电感的寄生电容(Cpst)从公布的SRF典型值计算得到,但需要增加额外的0.1pF,以代表与PCB焊盘有关的寄生电容。电容模型中的寄生电感(Lpst)遵循供应商软件中提供的值。