- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何在集成电路中减少天线效应

录入:edatop.com 点击:

布局对充电损伤的影响

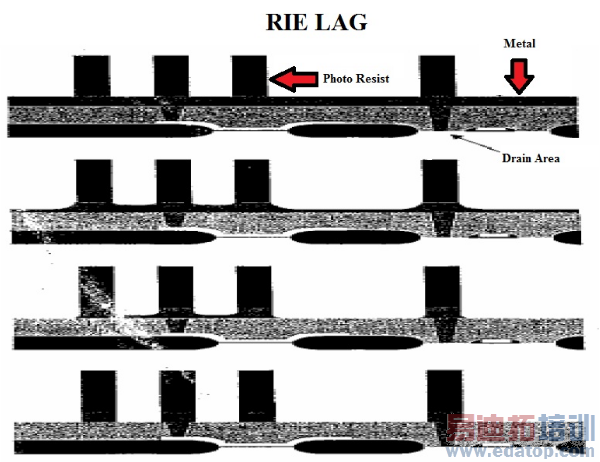

充电损伤的程度是一个几何函数,与极密栅线天线相关。但是由于刻蚀率的差异反映出的刻蚀延迟、等离子灰化和氧化沉积以及等离子诱导损伤(PID)的原因,使得充电损伤更容易受到电子屏蔽效应的影响。

图2:布局对充电损伤的影响。

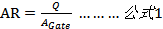

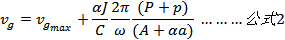

因此,天线效应的新模式需要考虑刻蚀时间的因素,如公式1。而通过插入二极管或桥(布线)控制天线效应,可以更好地预测天线效应,如公式2所示。

其中, Q指在刻蚀期间,向栅氧化层注入的总积累电荷。

A为导电层面积,等离子电流密度J下的电容容量为C

a为栅极面积,等离子电流密度J下的电容容量为a

α为电容比

P为天线电容器的周长

p为栅电容器的周长

ω为等离子电源的角频率

根据基于PID的新模式,PID不取决于AR,但是天线电容与栅极电容的比例是PID的良好指标。PID取决于等离子电源的频率,当氧化层<4nm,PID将对应力电流变得不敏感。在不增加J的情况下,增加栅极的介电常数,可增加PID。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:物联网中的水和电力

下一篇:Miracast实现大小设备间的无缝视频共享