- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

适用于2G/3G/4G的无线终端基带芯片

4. SL3000系统架构介绍

SL3000芯片是简约纳基于对2G/3G/4G终端基带系统的理解,设计实现完成的一颗多模芯片。不同于定制电路(ASIC)的设计思路,SL3000的物理层采用分布式的多个向量处理器的架构,适用于2G/3G/4G多个不同的物理层算法运行;另外一个子系统也是由多个可编程的内核构成,以便于高层多模协议栈软件运行。这两个子系统独立运行在不同的时钟域,根据系统负载可以采用各自最合适的工作频率。

4.1 SL3000的系统框图

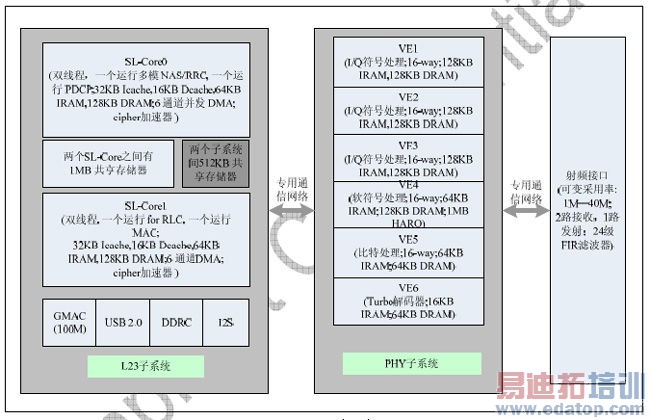

图5:SL3000的系统架构

4.2 SL3000子系统功能简介

如图5所示,SL3000内部分为两个大的子系统:L23子系统和PHY子系统。L23子系统由两个SL-Core构成,每个SL-Core子系统中有独自的Cache和RAM,以及DMA控制器和加解密模块。两个SL-Core之间有1Mbytes的共享内存。L23子系统还包含100M的GMAC控制器,USB2.0控制器,DDR 控制器等外设接口,为高速的数据通路提供接口。内核子系统与外设之间通过专有的网络互联互通。

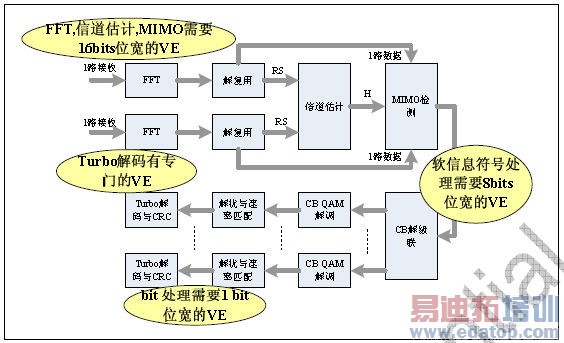

图6:不同信号处理要求不同的矢量处理器结构

PHY子系统由6个VE(Vector Engine)构成。如图6所示,由于在不同的信号处理阶段,信号本身具有不同的特征,需要矢量处理器也具有不同的特征。

其中三个VE是并行处理16位位宽的数据处理器,适用于通信链路中的I/Q数据处理的算法(例如均衡,匹配滤波,MIMO检测,FFT等等);一个VE是并行处理8位位宽的数据处理器,适用于通信链路中的软符号的处理(例如QAM解映射,HARQ软合并等算法);一个VE是并行处理1位位宽的数据处理器,适用于比特编解码算法(例如CRC计算,加解扰等);一个是Turbo解码器,适用于3G/4G中的Turbo码的处理。按照链路处理的需求,比特处理的VE也承担整个物理层调度的功能,它可以通过特定接口访问其他几个VE的内存空间,方便进行整个流程与时序的控制调度。其他几个VE两两之间有特定的通路进行通信互联,以便于数据在多个VE之间按照流水线处理的环节自然流畅地传输。

RFIF接口模块可以适应采样率从1MHz到40MHz的范围,有两个接收通路和一个发射通路,可灵活处理有无MIMO的射频前端接口。同时RFIF模块内有可编程的基准时钟模块,可以通过改变外部输入PLL的基准时钟和时钟倍频参数,提供不同的2G或3G或4G的系统时钟。RFIF模块中有专门的DMA引擎,可以自动完成对外接口与内部存储器之间的数据传输。这里的内部存储器包括了其中两个VE的内存空间和VE之间共享的一块专门的数据存储空间。这个专门的数据通路的设计,为基带数据的输入和输出提供了足够的带宽资源。

L23子系统与PHY子系统之间也通过专有的网络互联。且有一块特定的共享内存挂在这个网络上,L23 子系统的内核与DMA、PHY子系统的VE和DMA也都可以对此共享内存进行访问。这个特定的网络通路和共享内存区域为L23子系统与PHY子系统之间进行大量数据传输提供了足够的带宽资源。

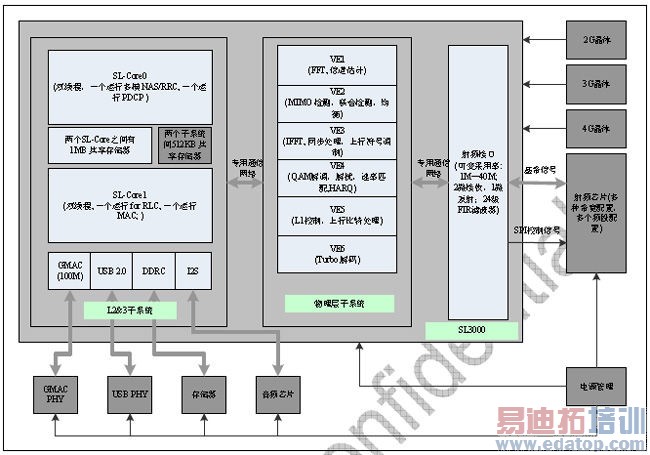

图7:基于SL3000构建多模终端参考方案

图7表达了基于SL3000的架构,可构成多模终端的方案。RFIF接口可连接一颗多频段多带宽可配置的射频芯片。语音可以走I2S接口与外部的语音处理芯片构成的通路,数据既可以走USB 接口也可以走GMAC接口。L23子系统有足够的能力运行多模的协议栈,PHY 子系统也有足够的能力运行多模的物理层软件。除了在上行和下行链路的局部直连总线外,没有复杂的多核互连网络。这样搭建的是一个简洁的,低成本低功耗的多模终端方案。

下一页:多模运行性能报告