- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种高效网络接口的设计

摘要:为了得到比传统片上网络的网络资源接口(NI)更高的数据传输效率和更加稳定的数据传输效果,提出了一种新的高效网络接口的设计方法,并采用Verilog HDL语言对相关模块进行编程,实现了高效传输功能,同时又满足核内路由的设计要求。最终通过仿真软件Xilinx ISE Design Suite 12.3和ModelSim SE 6.2b得到了满足设计要求的仿真结果。

关键词:片上网络;网络资源接口;核内路由;Verilog HDL

O 引言

随着纳米时代的到来,集成电路工艺不断的发展,特别是VISI设计技术的进步,系统级芯片的设计迎来了巨大的挑战,而这个挑战的的关键就是怎么样实现更高的通信效率。这个问题的出现也预示着多核技术时代的到临。为了应对这个挑战,人们提出了片上网络(Network On Chip,NoC)的概念。片上网络(NoC)移植了网络通信的方式,进而来解决多核时代的IP核互联通信的问题。

由于片上网络(NoC)具有优秀的可扩展性和相对较好的功耗效率,目前已经被大多数人认为是解决当前甚至未来芯片设计中关于通信问题的最重要的技术之一。

1 NoC简介

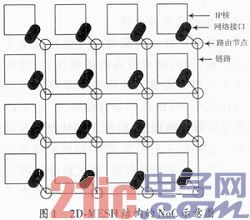

图1为传统2D-MESH结构的NoC示意图。图中明显可以看出片上网络(NoC)主要由4部分组成:资源节点(IP核)、路由节点、网络接口NI(Network Interface)和全局链路。其中网络接口NI就是连接IP核与通信网络的桥梁,同时网络接口NI的设计也是片上网络(NoC)设计技术中重要的一环。

网络接口NI使NoC实现了计算资源与通信网络部分的分离,允许IP核和网络通信结构分别独立进行设计,使计算资源相对网络更加透明,从而实现不同资源间的互联,提高了设计的重用性。网络接口NI主要面向地址信号,数据的打包、解包、编码,同步等方面的问题。文献提出的是一种既满足担保服务又满足最大努力服务的网络接口NI,但是此网络接口NI主要应用于AEthereal系统中。文献介绍了一种以OCP从模块存在的网络接口,应用于XpIPes系统。

2 通用网络接口NI的结构及模块功能

网络接口的作用主要基于网络中关于信息包信息的传输,并且将其转换成资源模块可用的形式。它的主要功能包括3个方面:提取关于IP核与网络之间的通信协议;支持任何IP核与网络接口连接;对数据进行打包和解包。

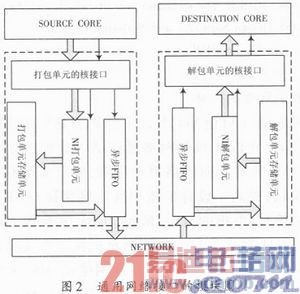

当数据在NoC中传输时,网络接口将主IP核中的数据进行打包,并进行校验,然后将其传输到路由节点进入网络,最后由目的IP核的网络接口进行解包,校验进入到目的IP核中。图2是通用网络接口的结构模块图,如图2所示其主要由通用核接口、数据打包单元、数据解包单元、存储单元和异步FIFO构成。数据打包单元主要将来自IP核的信息进行打包,其首先将信息转换成流控单元(flit),然后在网络中进行传输,其主要由包头编码单元,数据处理单元和FIFO控制单元构成。而解包单元主要是将数据包进行转换,满足目的IP核所需要的数据形式。数据打包单元和数据解包单元共享网络接口中的存储单元,这样做主要是易于链接不同模块。

3 高效网络接口的设计

3.1 总体结构的设计与分析

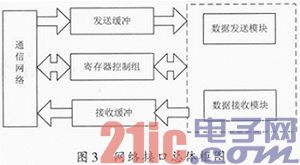

本文主要是设计一种高效的网络接口使其满足数据的快速传输,同时能承受高的通信压力,使其也可用于核内路由的数据传输。核内路由及将传统的路由节点嵌入到IP核中,与IP核共享存储单元,益于IP核与网络通信部分数据传输加速,以便于加快整个NoC的网络通信速率。据文献可知,核内路由也将是NoC发展的重要方向之一。如图3所示,本文设计的网络接口主要包含数据接收,数据发送,缓冲区模块和寄存器控制组4部分。

当原始数据从IP核传输到本网络接口,首先由数据接收模块将原始数据打包,并将其分为多个片(flit)。通常数据包被分为:Head flit,Datel flit,Date2 flit,Tailflit等4部分,而本网络接口将其压缩为Head flit,Datel flit,Date2 and control flit三部分,主要是将Tailflit压缩到传统Data2 flit中,因为Tail flit中只含有一个完成控制信号,所以将其合并到最后一个数据片上,通过寄存器控制模块控制发送,通过网络到达目的网络接口,由其将接受到的数据包进行解包,满足目的IP核的需求,同时传输到目的IP核。由于本网络接口也可以嵌入到IP核中,因此可以提前将Head flit发送出去,使Head flit的发送与数据打包并行处理。这样就加速了数据的传输速率。

3.2 数据接收模块的设计

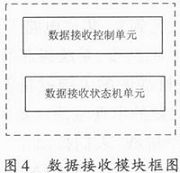

此模块主要是完成接收路由节点发出来的数据包以及本地IP核发出的数据包。其结构如图4所示,由数据接收逻辑控制模块和数据接收状态机模块。

此模块主要工作流程为:接收控制逻辑模块→产生缓存地址和有效信号→状态机模块→产生接收数据的状态。简单状态图如图5所示。

当系统复位,整个状态机处于空状态(idle),当同时接收到有效的数据信号和信道控制信号时,进入接收数据长状态(r_length)。随着clk上升沿的到达,顺序进入接收数据目的地址的状态(r_desti_addr),接收源地址状态(r_source_addr),接收数据状态(r_receive)。数据接收完成后,置数据传输完成信号无效后,状态机恢复初始状态(idle)。

3.3 数据发送模块的设计

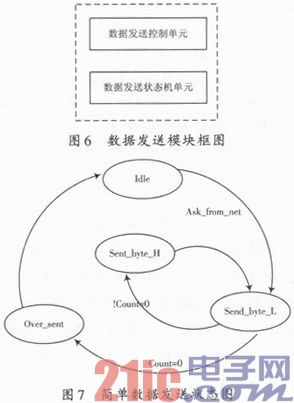

此模块主要是将从路由节点得到的数据发送给IP核,或者是将从IP核得到的数据传输到通信网络中去。设计思路同数据接收模块相似。结构图如图6所示分为2部分:数据发送控制逻辑模块和数据发送状态机模块。其状态机的转移图如图7所示。简述:idle→(有效数据发送信号)ask(信道请求信号)→(响应信道请求)buf_en→(clk上沿)t_length→t_date→(数据信号完成响应)idle。

3.4 寄存器控制组模块的设计

此模块主要分为:状态寄存器,逻辑控制寄存器,接收数据长寄存器,接收数据源地址寄存器。4个寄存器都为8位寄存器。满足了各节点对网络接口的控制。表1为状态寄存器。

当前网络接口的工作状态有表中寄存器的低两位所代表。"0"代表处于r_date,"1"代表处于s_date。

4 系统仿真与验证结果

本文设计的网络接口主要是使用Xilinx ISE Design suite 12.3和ModelSim SE 6.2b仿真软件进行仿真和验证。图8是网络接口中数据接收模块功能仿真图,图9是数据发送模块功能仿真图。实验主要是通过主时钟控制数据的发送,采用50 MHz的时钟,每2个时钟发送一个IP核数据,发送完成的到flag标识。从结果可以看出此设计便于加快数据在网络中的传输效率。实验中源IP核输出数据为32位,通过NI1把数据分为高16位和低16位输出,到达目的NI2,通过NI2把数据合并为32位,最终输入到目的IP核内。结果显示,数据传输过程数据保持了较强的稳定性,同时发送与接收都准确的做出了应答,达到了设计要求。

5 结语

本文设计的网络接口主要是针对对数据传输速率要求较高,对传输效果稳定性要求较高的NoC体系。通过实验基本实现了设计要求,同时此网络接口具有较强的实用性,对与今后核内路由的研究具有重要的意义。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:机载计算机RS422A通讯的软硬件设计与实现

下一篇:地铁车地通信数据传输系统设计