- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

机载计算机RS422A通讯的软硬件设计与实现

摘要 RS422A、RS485等异步串行通讯技术广泛应用于机载计算机实时控制系统,提高了飞机的可维护性和可扩展性。为使其稳定工作,不仅需要可靠硬件平台,还需严密的软件算法°文中描述了某机载计算机为实现与多个设备进行实时异步串行通讯,设计了统一的硬件平台,并根据每个设备不同的通讯协议,给出了不同的软件算法,重点阐述了软件设计及原理。根据该原理研制的产品已经过试验、联试和用户使用,证明其工作可靠、性能良好。

关键词 RS422A;RS485;通讯软件设计

1 RS422A标准

RS422A是一种在工程中广泛使用的接口标准,其采用差分传输方式,也称为"平衡传输",标准全称是"平衡电压数字接口电路的电气特性"。可见RS422A定义的是接口电路的电气特性,而对数据格式未作定义。RS422A是全双工通信,通信的双方均含有一个发送、接收驱动器。其中接收驱动器的两个平衡线连接端点定义为A和B,发送驱动器的两个平衡线连接端点定义为Y和Z,通常使用平衡双绞线将一端的Y和A、Z和B相连。通常发送驱动器端Y、Z之间的正电平在2~6 V,代表正逻辑,负电平在-6~-2 V,代表负逻辑。在接收端,当A、B之间有>+ 200 mV的电平时,输出正逻辑电平<-200 mV时,输出负逻辑电平。RS422A最大传输距离为4 000英尺(约1 219 m),最大传输速率为10 Mbit· s-1。其中平衡双绞线的长度与传输速率成反比,在100 kbit·s-1速率下,才可达到最大传输距离。只有在较短的距离下才能获得最高速率传输。一般100 m长的双绞线可获取的最大传输速率为1Mbit·s-1。

2 硬件设计

对于RS422A、RS485等异步串行通讯的硬件设计,主要有两种方式。

(1)采用协议芯片加接口驱动芯片的方式。该方式技术较成熟,但使用的元器件较多,占用印制板的板面较大。

(2)采用SOC的方式,将协议芯片的逻辑功能在可编程逻辑器件FPGA中编程实现。该方式使用的元器件较少,但在FPGA中写出较完善的协议逻辑的难度较大。

本工程中采用第一种方式,用协议芯片16C552或16C554加接口驱动芯片进行通讯。并设计回绕自测试电路。采用16C552芯片实现全双工收发RS-422器功能,RS-422驱动电路由DS26LS31MJ(4路RS-422发送器)、DS26LS32MJ(4路RS-422接收器)、终端匹配电路和保护电路组成。

3 软件设计

3.1 通讯协议的定义

RS422A标准只对接口的电气特性做出规定而不涉及协议,因此可定义自身的高层通信协议。在本设计方案中,在底层以Byte为单位通信,采用UART字的格式。在上层协议中采用数据包为单位通信。

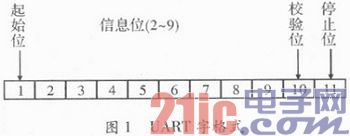

通信协议中主要规定:(1)通讯双方的传送控制方式,即主从命令响应方式或周期通讯方式等。(2)通讯周期。(3)通讯速率,即波特率。(4)通讯字格式。通讯的最小信息单位是UART字,每个UART字由11位二进制数组成,如图1所示。

第1位:起始位(逻辑"0"状态为有效);第2~9位:信息位;第10位:奇偶校验位(约定为偶校验);第11位:停止位(逻辑"1"状态为有效)。每个UART字按低位到高位的先后顺序串行传送。对于16位二进制数据分成两个UART字,按由低到高的先后顺序传送。(5)通讯包格式。通讯传送的基本单位是通讯包,通讯包由包头、包状态、数据字和包尾组成,最后的包尾是校验和字,其结构如图2所示。

校验和字为通讯包中除校验和字外所有字累加和的补码。校验和校验正确的依据为接收到的UART字块中所有字的累加和等于0。

包头通常规定为0xAA55或0x55AA,与数据字相同的概率较小。包头一旦与数据字相同,则可能误认为该数据字为包头,从而组包错误。

通讯协议应规定每个数据字中每一位的定义。若通讯协议中存在多种包长或多种数据包定义,则应在包状态中说明该包的包长或包序号,由包序号可明确该包数据的详细定义。

3.2 接收数据

首先,需确定接收数据的方式,即选择查询接收或是中断接收。嵌入式实时控制系统应尽量减少中断的使用,在查询接收可满足通讯要求,且不影响实时性的情况下,尽量采用查询的方式接收数据。

若通讯协议规定,要接收的数据包的长度小于或等于硬件接收FIFO缓冲区的长度,且两包数据间的间隔时间大于或等于最小查询周期,则可采用查询的方式接收数据。否则需采用中断的方式接收,才能保证数据不丢失。

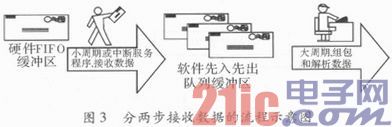

采用查询的方式接收数据时,以最小周期进行反复查询,若硬件接收FIFO缓冲区中有数据则收入软件中设定的容量较大的先入先出队列缓冲区。

采用中断的方式接收数据时,硬件接收FIFO缓冲区中有数据则会引发中断,中断服务程序中将硬件接收FIFO缓冲区中有数据则收入软件中设定的容量较大的先入先出队列缓冲区。

而后,再以通讯协议规定的接收数据周期,从软件队列缓冲区中取数、找包头、按包长组包、算校验和。当未收到完整数据包或校验和错时,进行错误计数。

上述分两步接收数据的流程示意如图3所示。以该方式,可无需消耗多余的时间,并确保数据不丢失。

3.3 发送数据

发送数据作为主动的行为,尽量不使用中断。当需发送的数据包长度小于或等于硬件发送FIFO缓冲区时,可直接发送。当需发送的数据包长度大于硬件发送FIFO缓冲区时,可分为多次发送。软件将要发送的数据组织好后存入容量较大的先入先出队列缓冲区。再以软件运行的最小周期,将队列缓冲区中的数据分批装入硬件发送FIFO缓冲区进行发送。

4 数据组包的算法

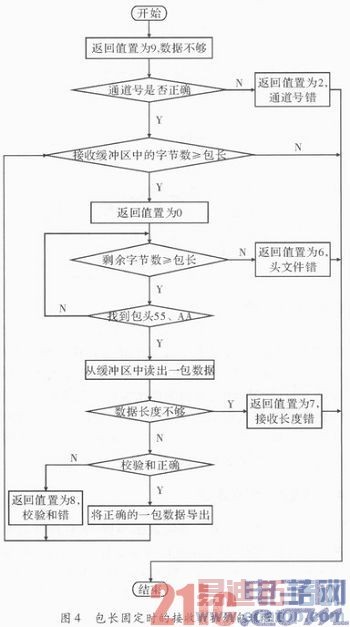

以通讯协议规定的接收数据周期,从软件队列缓冲区中取数,进行数据组包的算法是较为重要的,其保证了软件采信数据的有效性和完整性。并和通讯协议密切相关。包长固定时的流程如图4所示,其主要步骤如下:

(1)确认要接收的通道号是否合法。

(2)在软件队列缓冲区中,当剩余字节数大于等于包长时,才有可能取得新的一包完整数据。剩余字节数小于包长则认为无新的一包完整数据,等到下个周期再组包接收。

(3)在剩余字节数大于等于包长的条件下,按照通讯协议中规定的包头,从队列中依次查找,非包头则抛掉,直至找到包头。

(4)以包头为起始,按包长取出一包数据,计算校验和。若校验和正确则得到一包有效数据。

(5)软件队列缓冲区中若还有足够数据,则继续查找包头并组包,若有新的一包有效数据则采用最新数据,防止数据积压。

用该算法,当有错误数据出现时,可检查出错误并丢弃出错的数据包,找出下一包正确的数据。不会因一包数据出错而影响后续多包数据。

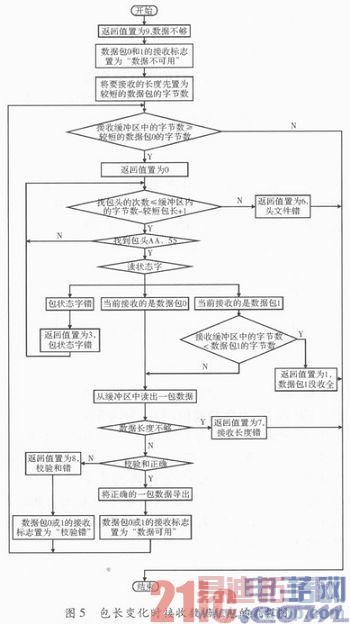

要接收的数据包长变化时,通讯协议需规定,根据包头后的包状态字明确该包数据的包长。先假定当前要接收的是最短包,以缓冲区中剩余字节数大于或等于最短包长,作为找包头的前提条件。找到包头后,根据包状态字确定该包包长,若缓冲区中剩余字节数小于该包包长,则认为数据未完成接收,将包头和包状态字仍留存在缓冲区中,等待下个周期补充新数据后再进行组包接收。包长变化时接收数据组包的流程较复杂,如图5所示。

5 结束语

文中设计的算法充分考虑了传输过程可能出现的各种情况,分两步完成数据接收,小周期或中断仅进行硬件缓冲区的接收,满足实时性要求且保证数据不会因未及时接收而丢失;大周期进行数据组包,并以最快捷的方式找到有效数据包。系统与12个设备进行RS422A或RS485通讯,经验证,文中设计的算法综合机载计算机实时控制系统的实时性和可靠性要求。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇: 校园无线视频监控系统的设计与应用

下一篇:一种高效网络接口的设计