- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于叠加训练序列光OFDM系统帧同步算法FPGA实现

摘要:光纤通信系统中引进OFDM技术给O-OFDM系统带来对同步、高峰均比等敏感问题。叠加训练序列技术时IM/DDO-OFDM系统帧同步算法研究,设计了FPGA的算法实现结构,联合Matlab,Modelsim等仿真工具验证算法开发的有效性。实验结果表明,叠加的训练序列对数据影响较小,与传统方法相比,具有更高的同步正确率,易于实现,有较强的工程应用前景。

关键词:叠加训练序列技术;OFDM;帧同步;Modelsim

0 引言

正交频分复用技术OFDM是一种特殊的多载波传输方式,具有抗多径能力强、频谱利用率高、适合高速数据传输等优点,因此已被广泛地应用于最新的无线通信系统中。本文设计基于叠加训练序列的多模光纤IM/DDO-OFDM系统帧同步算法。QuartusⅡ软件仿真平台和Verilog HDL硬件描述语言进行训练序列的产生、训练序列与数据符号的叠加运算,以及进行帧同步算法实现。其Modelsim仿真实现帧同步结果与Matlab仿真实现的结果一致,为实际的工程设计提供了可靠的依据。

1 系统模型

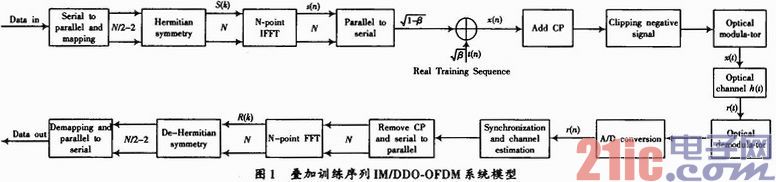

为了满足系统传输实信号的要求,将二进制数据流经过星座图映射(如:M-QAM或QPSK)后进行厄米特共轭对称(Hermitian Symmetry,HS)变换,使得经过快速傅里叶逆变换(Inverse Fast Fourier Transform,IFFT)后得到双极性实信号。叠加训练序列IM/DDO-OFDM系统模型如图1所示。

2 叠加训练序列设计及帧同步方法

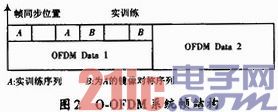

一个数据帧可以包含多个OFDM符号,实现帧同步主要是为了确定接收端数据帧的起始位置。通过把已知的训练序列叠加在一个完成OFDM符号上,包含两个O-OFDM数据符号的系统帧结构如图2所示。

假设所要设计的训练序列长度为N,根据以下步骤可以构造出单极性实训练序列。

步骤1:设计一个自相关性良好的序列A,长度为L,且L<

步骤3:取长度为L的序列B的实部或者虚部作为序列C;

步骤4:将双极性序列C变成单极性序列D(将小于0的信号置0);

步骤5:将D进行简单的重复m/2次,形成序列E,即:EN/2=[D D…D];

步骤6:将序列E进行镜像变换得到镜像序列F;

步骤7:将原序列E和镜像序列F构成长度为N的训练序列T,即:EN=[EN/2 FN/2]。

根据上述7个步骤所设计出的训练序列EN前后两部分均具有周期性,采取同时采用了镜像特性进行构造,这使得后续设计的帧同步算法可以降低计算复杂度,而且在同步性能上也更具优势。

将所设计好的训练序列线性叠加在一个完整的O-OFDM符号上,并对训练序列和被叠加的O-OFDM符号进行功率分配,其中训练序列分配弱能量。接收端,通过本地弱能量序列与处理后的接收信号进行互相关获取帧同步。

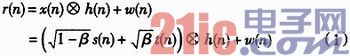

经叠加后的帧信号经过多模光纤信道后,接收端的模数转换后的信号r(n)可以表示为:

式中:"![]() "表示循环卷积;h(n)表示多模光纤信道脉冲响应;w(n)表示电域高斯白噪声;s(n)表示发送数据;t(n)为训练序列,且训练序列结构上满足上述EN镜像对称性,β表示功率能量分配因子,

"表示循环卷积;h(n)表示多模光纤信道脉冲响应;w(n)表示电域高斯白噪声;s(n)表示发送数据;t(n)为训练序列,且训练序列结构上满足上述EN镜像对称性,β表示功率能量分配因子,![]() 和

和![]() 分别表示训练序列和发射数据的功率。

分别表示训练序列和发射数据的功率。

在式(1)中,训练序列分配的能量非常弱,为了使同步时刻的能量能够足够大,而不受其他旁瓣干扰,先对接收信号r(n)进行处理。截取长度为N的接收信号,利用式(2)进行变换得到新的接收信号z(n)。

z(n)=r(n)+r(N-n+1) (2)

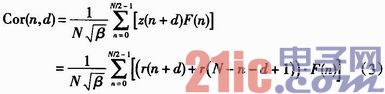

变换后得到的新序列z(n)具有原序列两倍的能量,与本地训练序列F进行互相关,来获取同步。帧同步函数可以表示为:

式中:d为整数,表示接收信号序列与本地序列之间的相对滑动位置,N/2为相关长度。采用的训练序列具有良好的自相关性和弱互相关性,当d滑动到同步位置时刻,帧同步函数Cor(n,d)达到最大值,其余时刻为幅度较小的随机信号。

为了降低接收机同步设计的复杂度,采用预设门槛值T,当检测器的输出Cor(n,d)满足式(4),P(n)表示接收信号的功率,则此刻的d达到帧同步位置。

|Cor(n,d)|2>T·P(n) (4)

3 算法性能Matlab仿真分析

仿真参数主要包括:发送数据比特流为10 Gb/s,调制方式为16-QAM,系统子载波数为256,光纤链路部分采用1 310 nm的多模光纤,衰减常数α=0.2 dB/km,考虑色散效应,取值为17 ps/(nm·km),PIN光电检测器的灵敏度设定为1 A/W,暗电流为10 nA。以下的仿真结果基于10 000次蒙特卡罗仿真。

3.1 功率分配因子与BER性能

通过不同信噪比下的系统BER性能及不同功率分配因子下的算法同步正确率仿真综合得出最佳功率分配因子,仿真结果如图3,图4所示。

从图3,图4可以看出,当功率分配因子逐渐增大时,意味着叠加在数据OFDM符号上的能量越来越大,使得目标函数的能量值越大。但系统的BER性能变得越来越差,相反算法的同步性能变得越来越好。权衡两者性能,选择最佳功率分配因子β=0.05,后续将以此功率分配因子为基础进行仿真。需要说明的是,仿真系统BER性能的时候,将叠加训练序列作为干扰信息,没有进行信道估计,因此图3中不会出现极值现象。

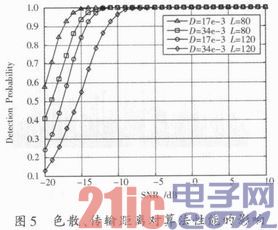

3.2 同步性能仿真比较

图5中给出了色散系数分别为17 ps/(nm·km)和34 ps/(nm·km)下不同传输距离的算法同步性能仿真。D表示色散系数,L表示传输距离。可以看出,相同色散下,传输距离越长,光能量损耗越大,使得算法同步性能变差;同时相同传输距离下,不同色散系数对算法的同步性能也将产生影响,色散系数越大,使得同步性能变差。由此可以判断在光OFDM系统中,光纤的色散和传输距离会影响算法的同步性能。

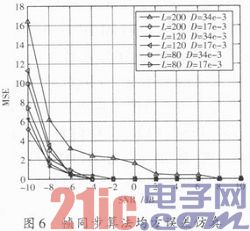

为了更加突出帧同步算法性能的优越性,图6将通过仿真验证算法的均方误差(Mean Square Error,MSE)性能。可以看出,算法随着信噪比的增大,趋近于稳定,收敛性较快。在信噪比大于-2 dB的情况下,算法性能稳定。

构造的训练序列具有良好的自相关性能,同时对于接收信号进行简单的移位截取镜像叠加处理,把长序列相关转换为短序列相关,降低了计算量,减少硬件资源的消耗。文献中采用长度为512的m序列,算法2采用了两次循环嵌套的累积求和方法,算法3利用求平均的方式,而本文采用长度为256的序列,将截取长度为512的接收信号进行镜像叠加处理,把长序列的乘积转化为短序列的乘积,降低了使用乘法器的次数,同时采用的训练序列比文献中的要短。因此,本文的同步算法在计算复杂度上比文献中的算法2和算法3更具优势。

4 帧同步算法的FPGA仿真实现

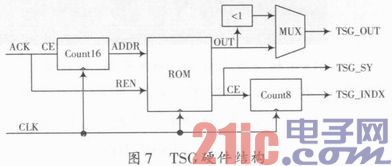

4.1 训练序列产生

训练序列产生(Training Sequence Generator,TSG)模块的硬件实现结构如图7所示。TSG采用频率为20 MHz时钟进行基带处理。从微处理器送出的控制信号ACK用来启动TSG模块的工作。与IM/DDO-OFDM符号长度N(N=64)保持一致,ACK信号持续拉高1 025个时钟,一共持续完成64个周期的训练序列输出,每个周期内有16个时域样值。其中,TSG模块输出数据采用8位带符号的二进制表示,后8个周期TSG模块输出数据与前8个周期输出的数据具有镜像对称关系。

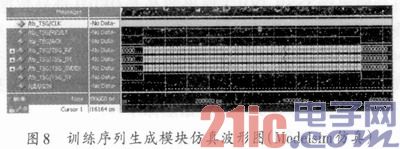

经过综合、布局、布线后仿真,得出TSG工程文件的Modelsim仿真如图8所示。

每个TSG周期的16个时域样值存储在FPGA片内的ROM中。其中高8位为训练序列样值的实部,低8位为训练序列样值的虚部。由图8可知,当ACK信号为高时,Count16开始计数1 025个时钟,产生的地址信号控制ROM将存储的16个时域训练序列采样值读取,先重复m/2(m=8)个周期,形成训练序列的前半部分,再重复8个周期,形成训练序列的后半部分,最后组合成所需要的叠加训练序列。从输出部分可以看出,TSG_SY信号与TSG模块输出的训练序列实部和虚部样值保持同步。

4.2 训练序列叠加方式的FPGA实现

根据图1叠加训练序列IM/DDO-OFDM系统模型利用FPGA设计实现训练序列与光数据OFDM符号的叠加。在保持发射功率不变,分别对训练序列和光数据OFDM符号进行了功率分配。训练序列叠加(TSSP)模块主要端口说明:TSSP_CLK:工作时钟,频率为20 MHz;OOFDM_DIN:被叠加的光OFDM符号数据帧;TSG_DIN:训练序列实部或者虚部;POWER_CT:叠加功率分配控制,保持发射机功率不变;TSSP_ACK:高电平有效,控制OOFDM_DIN和TSG_DIN的输入;TSSP_DOUT:TSSP模块输出信号;TSSP_INDEX:叠加信号输出的坐标序号;TSSP_RDY:TSSP输出有效,与OOF DM_DIN信号同步。

经过综合、布局、布线后仿真,得出TSSP工程文件Modelsim仿真如图9所示,局部放大结果见图10。

从图9,图10可以看出,未叠加前,信号输出端TSSP_DOUT输出的是光OFDM符号数据,TSSP_RDY信号持续低电平;信号叠加时,TSSP_RDY信号持续高电平,信号输出端TSSP_DOUT输出的是经过功率控制后的叠加信号;叠加操作完成后,TSSP_RDY信号被拉低,信号输出端TSSP_DO UT输出的是光OFDM符号数据。叠加输出的信号TSSP_DOUT与输入的信号OOFDM_DIN和TSG_DIN持续的周期一致,且保持8个数据位长度。在输出部分,TSSP_INDEX输出训练序列与O-OFDM符号叠加后的数据坐标序号。

4.3 帧同步仿真实现及性能分析

帧同步模块的外部接主要端口说明:INEN同步的输入数据有效信号,与数据同步;BITINREC:处理后的接收信号;BITINTSG:本地训练序列;CORRLETAIONSUM:帧同步输出数据;INDEX:帧同步输出数据的坐标序号;OUTEN:帧同步后输出数据有效信号。

Modelsim仿真软件得到仿真结果如图11所示。CORRLETAIONSUM为接收信号经过处理得到的BITINREC与本地训练序列BITINTSG进行互相关运算的累加和,DOUTEN为帧同步后(即相关运算累加和值大于预设门限值),同步拉高。图12为帧同步归一化Matlab仿真图。从图11中可以看出,输出信号CORRLETAIONSUM与图12中的相关峰值归一化结果基本一致,验证了帧同步算法在FPGA上实现的可能。判断依据是在图11中有个DOUTEN信号和INDEX信号,其中DOUTEN信号表示的搜索到最大值时刻进行同步信号拉高处理,INDEX信号为帧同步相关后的坐标序号输出值。在DOUTEN信号输出电平拉高的时候,刚好INDEX信号的值为153,而相同参数下Matlab仿真的波形输出最大值的坐标也为153,当这两个值相等的时候,可以判断两个仿真波形输出是一致的。

5 结语

本文设计的重点和难点是叠加训练序列设计、FPGA平台的构建,研究了叠加训练序列光OFDM帧同步算法。并详细阐述了各模块的具体FPGA实现方法,提高了同步的精度。最终通过Matlab和Modelsim完成了目标算法的工程实现。验证了帧同步算法在FPGA上实现的可能,将逐步被应用于各种工程中。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:基于ATmega16的数字旋转变压器设计

下一篇:一种突发OFDM传输系统的设计